## HIGH PERFORMANCE SINGLE CHIP 8-BIT MICROCOMPUTERS

### **DESCRIPTION**

The NEC  $\mu$ PD8049 and  $\mu$ PD8039L are single chip 8-bit microcomputers. The processors differ only in their internal program memory options: the  $\mu$ PD8049 has 2K x 8 bytes of mask ROM and the  $\mu$ PD8039L has external program memory. Both of these devices feature new, high performance 11 MHz operation.

### **FEATURES**

- High Performance 11 MHz Operation

- Fully Compatible with Industry Standard 8049/8039

- Pin Compatible with the μPD8048/8748/8035

- NMOS Silicon Gate Technology Requiring a Single +5V ±10% Supply

- 1.36 μs Cycle Time. All Instructions 1 or 2 Bytes

- Programmable Interval Timer/Event Counter

- 2K x 8 Bytes of ROM, 128 x 8 Bytes of RAM

- Single Level Interrupt

- 96 Instructions: 70 Percent Single Byte

- 27 I/O Lines

- Internal Clock Generator

- Expandable with 8080A/8085A Peripherals

- Available in Both Ceramic and Plastic 40-Pin Packages

### PIN CONFIGURATION

| TO | μPD<br>8049/<br>8039L | 40  VCC 39  T <sub>1</sub> 38  P27 37  P26 36  P25 35  P24 34  P17 33  P16 32  P15 31  P14 30  P13 29  P12 28  P11 27  P10 26  VDD 25  PROG 24  P23 23  P22 22  P21 21  P20 |

|----|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

7

### μPD8049/8039L

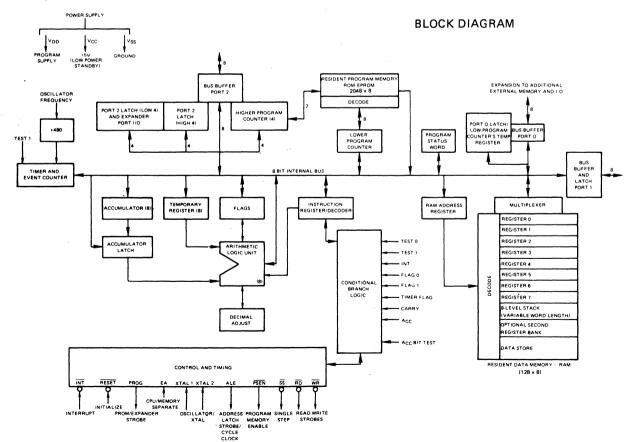

The NEC  $\mu$ PD8049 and  $\mu$ PD8039L are high performance, single component, 8-bit parallel microcomputers using N-channel silicon gate MOS technology. The  $\mu$ PD8049 and  $\mu$ PD8039L function efficiently in control as well as arithmetic applications. The powerful instruction set eases bit handling applications and provides facilities for binary and BCD arithmetic. Standard logic functions implementation is facilitated by the large variety of branch and table look-up instructions.

FUNCTIONAL DESCRIPTION

The  $\mu$ PD8049 and  $\mu$ PD8039L instruction set is comprised of 1 and 2 byte instructions with over 70 percent single-byte. The instruction set requires only 1 or 2 cycles per instruction with over 50 percent single-cycle.

The  $\mu$ PD8049 and  $\mu$ PD8039L microprocessors will function as stand-alone microcomputers. Their functions can easily be expanded using standard 8080A/8085A peripherals and memories.

The  $\mu$ PD8049 contains the following functions usually found in external peripheral devices: 2048 x 8 bits of mask ROM program memory; 128 x 8 bits of RAM data memory; 27 I/O lines; an 8-bit interval timer/event counter; and oscillator and clock circuitry.

The  $\mu$ PD8039L is intended for applications using external program memory only. It contains all the features of the  $\mu$ PD8049 except the 2048 x 8-bit internal ROM. The external program memory can be implemented using standard 8080A/8085A memory products.

## PIN IDENTIFICATION

|                 | PIN                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.             | SYMBOL                                       | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1               | т <sub>0</sub>                               | Testable input using conditional transfer functions JT0 and JNT0. The internal State Clock (CLK) is available to $T_0$ using the ENTO CLK instruction. $T_0$ can also be used during programming as a testable flag.                                                                                                                                                                                                                                                         |

| 2               | XTAL 1                                       | One side of the crystal, LC, or external frequency source. (Non-TTL compatible $V_{IH}$ .)                                                                                                                                                                                                                                                                                                                                                                                   |

| 3               | XTAL 2                                       | The other side of the crystal or LC frequency source. For external sources, XTAL 2 must be driven with the logical complement of the XTAL 1 input.                                                                                                                                                                                                                                                                                                                           |

| 4               | RESET                                        | Active low input from processor initialization. RESET is also used for PROM programming verification and power-down (non-TTL compatible V <sub>IH</sub> ).                                                                                                                                                                                                                                                                                                                   |

| 5               | ŜŜ                                           | Single Step input (active-low), \$\overline{SS}\$ together with ALE allows the processor to "single-step" through each instruction in program memory.                                                                                                                                                                                                                                                                                                                        |

| 6               | ĪNŦ                                          | Interrupt input (active-low), $\overline{\text{INT}}$ will start an interrupt if an enable interrupt instruction has been executed. A reset will disable the interrupt, $\overline{\text{INT}}$ can be tested by issuing a conditional jump instruction.                                                                                                                                                                                                                     |

| 7               | EA                                           | External Access input (active-high). A logic "1" at this input commands the processor to perform all program memory fetches from external memory.                                                                                                                                                                                                                                                                                                                            |

| 8               | ŔD                                           | READ strobe outputs (active-low). RD will pulse low when the processor performs a BUS READ. RD will also enable data onto the processor BUS from a peripheral device and function as a READ STROBE for external DATA MEMORY.                                                                                                                                                                                                                                                 |

| 9               | PSEN                                         | Program Store Enable output (active-low). PSEN becomes active only during an external memory fetch.                                                                                                                                                                                                                                                                                                                                                                          |

| 10              | WR                                           | WRITE strobe output (active-low). $\overline{\text{WR}}$ will pulse low when the processor performs a BUS WRITE. $\overline{\text{WR}}$ can also function as a WRITE STROBE for external DATA MEMORY.                                                                                                                                                                                                                                                                        |

| 11              | ALE                                          | Address Latch Enable output (active-high). Occurring once each cycle, the falling edge of ALE latches the address for external memory or peripherals. ALE can also be used as a clock output.                                                                                                                                                                                                                                                                                |

| 12-19           | D <sub>0</sub> -D <sub>7</sub> BUS           | 8-bit, bidirectional port. Synchronous reads and writes can be performed on this port using RD and WR strobes. The contents of the D0-D7 BUS can be latched in a static mode. During an external memory fetch, the D0-D7 BUS holds the least significant bits of the program counter. PSEN controls the incoming addressed instruction. Also, for an external RAM data store instruction the D0-D7 BUS, controlled by ALE, RD and WR, contains address and data information. |

| 20              | V <sub>SS</sub>                              | Processor's GROUND potential.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 21-24,<br>35-38 | P <sub>20</sub> -P <sub>27</sub> :<br>PORT 2 | Port 2 is the second of two 8-bit quasi-bidirectional ports. For external data memory fetches, the four most significant bits of the program counter are contained in $P_{20}$ - $P_{23}$ . Bits $P_{20}$ - $P_{23}$ are also used as a 4-bit I/O bus for the $\mu$ PD8243, INPUT/OUTPUT EXPANDER.                                                                                                                                                                           |

| 25              | PROG                                         | PROG is used as an output strobe for $\mu$ PD8243's during I/O expansion. When the $\mu$ PD8049 is used in a stand-alone mode the PROG pan can be allowed to float.                                                                                                                                                                                                                                                                                                          |

| 26              | V <sub>DD</sub>                              | $V_{DD}$ is used to provide +5V to the 128 x 8 bit RAM section. During normal operation $V_{CC}$ must also be +5V to provide power to the other functions in the device. During stand-by operation $V_{DD}$ must remain at +5V while $V_{CC}$ is at ground potential.                                                                                                                                                                                                        |

| 27-34           | P <sub>10</sub> -P <sub>17</sub> :<br>PORT 1 | Port 1 is one of two 8-bit quasi-bidirectional ports.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 39              | T1                                           | Testable input using conditional transfer functions JT1 and JNT1. T1 can be made the counter/timer input using the STRT CNT instruction.                                                                                                                                                                                                                                                                                                                                     |

| 40              | Vcc                                          | Primary Power supply. V <sub>CC</sub> is +5V during normal operation.                                                                                                                                                                                                                                                                                                                                                                                                        |

## μ PD8049/8039L

| Operating Temperature                               | ABSOLUTE MAXIMUM |

|-----------------------------------------------------|------------------|

| Storage Temperature (Ceramic Package)65°C to +150°C | RATINGS*         |

| Storage Temperature (Plastic Package)65°C to +125°C |                  |

| Voltage on Any Pin, - 0.5 to +7 Volts ①             |                  |

| Power Dissipation                                   |                  |

Note: 1 With respect to ground.

COMMENT: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

$T_a = 0^{\circ}C \text{ to } +70^{\circ}C; V_{CC} = V_{DD} = +5V \pm 10\%; V_{SS} = 0V$

| DC | CHA | ٩RAC | TER | IST | CS |

|----|-----|------|-----|-----|----|

|    |     |      |     |     |    |

|                                                            |                 | 1    | LIMIT    | s    |      |                                                             |  |  |

|------------------------------------------------------------|-----------------|------|----------|------|------|-------------------------------------------------------------|--|--|

| PARAMETER                                                  | SYMBOL          | MIN  | TYP      | MAX  | UNIT | TEST CONDITIONS                                             |  |  |

| Input Low Voltage<br>(All Except XTAL 1, XTAL 2)           | VIL             | -0.5 |          | 0.8  | ٧    |                                                             |  |  |

| Input High Voltage<br>(All Except XTAL 1, XTAL 2, RESET)   | ViH             | 2.0  |          | Vcc  | ٧    |                                                             |  |  |

| Input High Voltage<br>(RESET, XTAL 1, XTAL 2)              | VIH1            | 3.8  |          | Vcc  | ٧    |                                                             |  |  |

| Output Low Voltage (BUS, RD, WR, PSEN, ALE)                | VOL             |      |          | 0.45 | ٧    | I <sub>OL</sub> = 2.0 mA                                    |  |  |

| Output Low Voltage (All Other<br>Outputs Except PROG)      | VOL1            |      |          | 0.45 | ٧    | I <sub>OL</sub> = 1.6 mA                                    |  |  |

| Output Low Voltage (PROG)                                  | VOL2            |      |          | 0.45 | ٧    | I <sub>OL</sub> = 1.0 mA                                    |  |  |

| Output High Voltage (BUS, RD,<br>WR, PSEN, ALE)            | Vон             | 2.4  |          |      | ٧    | I <sub>OH</sub> = -100 μA                                   |  |  |

| Output High Voltage (All Other<br>Outputs)                 | Vон1            | 2.4  |          |      | ٧    | t <sub>OH</sub> = -50 μA                                    |  |  |

| Input Leakage Current<br>(T <sub>1</sub> , EA, INT)        | lıL.            | -    | . et<br> | ±10  | μΑ   | V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>         |  |  |

| Output Leakage Current<br>(BUS, To — High Impedance State) | <sup>I</sup> OL |      |          | ±10  | μА   | V <sub>CC</sub> ≥ V <sub>IN</sub> ≥ V <sub>SS</sub> + 0.45V |  |  |

| Power Down Supply Current                                  | IDD             |      | 25       | 50   | mA   | T <sub>a</sub> = 25°C                                       |  |  |

| Total Supply Current                                       | IDD + ICC       |      | 100      | 170  | mA   | T <sub>a</sub> = 25°C                                       |  |  |

PORT #1 PORT #2 RESET READ SINGLE WRITE STEP μPD EXTERNAL 8049/ PROGRAM STORE MEMOR 8039L ENABLE TEST ADDRESS LATCH ENABLE INTERRUPT PORT EXPANDER BUS STROBE

LOGIC SYMBOL

<sup>\*</sup>Ta = 25°C

# 7

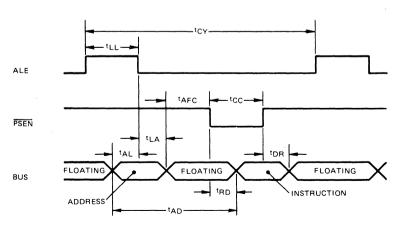

### AC CHARACTERISTICS

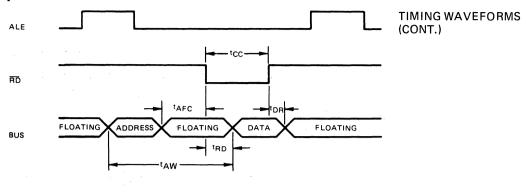

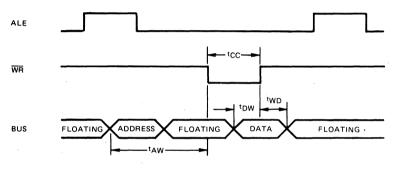

## READ, WRITE AND INSTRUCTION FETCH – EXTERNAL DATA AND PROGRAM MEMORY

$T_a = 0^{\circ} C \text{ to } +70^{\circ} C; V_{CC} = V_{DD} = +5V \pm 10\%; V_{SS} = 0V$

|                                    |                  | LIMITS |     |      |      | TEST                     |

|------------------------------------|------------------|--------|-----|------|------|--------------------------|

| PARAMETER                          | SYMBOL           | MIN    | TYP | MAX  | UNIT | CONDITIONS               |

| ALE Pulse Width                    | tLL              | 150    |     |      | ns   |                          |

| Address Setup before ALE           | <sup>t</sup> AL  | 70     |     |      | ns   |                          |

| Address Hold from ALE              | <sup>t</sup> LA  | 50     |     |      | ns   |                          |

| Control Pulse Width (PSEN, RD, WR) | tCC              | 300    |     |      | ns   |                          |

| Data Setup before WR               | t <sub>DW</sub>  | 250    |     |      | ns   |                          |

| Data Hold after WR                 | tWD              | 40     |     |      | ns   | C <sub>L</sub> = 20 pF 3 |

| Cycle Time                         | tCY              | 1.36   |     | 15.0 | μs   |                          |

| Data Hold                          | <sup>t</sup> DR  | 0      |     | 100  | ns   |                          |

| PSEN, RD to Data In                | <sup>t</sup> RD  |        |     | 200  | ns   |                          |

| Address Setup before WR            | tAW              | 200    |     |      | ns   |                          |

| Address Setup before Data In       | <sup>t</sup> AD  |        |     | 400  | ns   |                          |

| Address Float to RD, PSEN          | <sup>t</sup> AFC | -40    |     |      | ns   |                          |

Notes: 1) For Control Outputs: CL = 80 pF

② For Bus Outputs: C<sub>L</sub> = 150 pF

③  $t_{CY} = 1.36 \,\mu s$

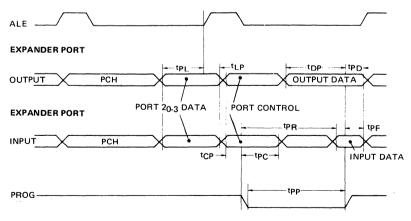

PORT 2 TIMING

$T_a = 0^{\circ} C \text{ to } +70^{\circ} C; V_{CC} = +5V \pm 10\%; V_{SS} = 0V$

|                                                   |                 |     | LIMIT | s   |      | TEST       |

|---------------------------------------------------|-----------------|-----|-------|-----|------|------------|

| PARAMETER                                         | SYMBOL          | MIN | TYP   | MAX | UNIT | CONDITIONS |

| Port Control Setup before Falling<br>Edge of PROG | <sup>t</sup> CP | 100 |       |     | ns   |            |

| Port Control Hold after Falling<br>Edge of PROG   | <sup>†</sup> PC | 60  |       | ,   | ns   |            |

| PROG to Time P2 Input must be<br>Valid            | t <sub>PR</sub> |     |       | 650 | ns   |            |

| Output Data Setup Time                            | t <sub>DP</sub> | 200 |       |     | ns   |            |

| Output Data Hold Time                             | tPD             | 20  |       |     | ns   |            |

| Input Data Hold Time                              | tPF             | 0   |       | 150 | ns   |            |

| PROG Pulse Width                                  | tpp             | 700 |       |     | ns   |            |

| Port 2 I/O Data Setup                             | tpL             | 150 |       |     | ns   |            |

| Port 2 I/O Data Hold                              | tLP             | 20  |       |     | ns-  |            |

### TIMING WAVEFORMS

INSTRUCTION FETCH FROM EXTERNAL MEMORY

## μPD8049/8039L

**READ FROM EXTERNAL DATA MEMORY**

WRITE TO EXTERNAL MEMORY

**PORT 2 TIMING**

|                |                                                                                           |                                                                                  |                                        |                     | INST                | TRUC      | TION C        | ODE                 |                     |                     |        | Γ     | FLAGS                                 |

|----------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------|---------------------|---------------------|-----------|---------------|---------------------|---------------------|---------------------|--------|-------|---------------------------------------|

| MNEMONIC       | FUNCTION                                                                                  | DESCRIPTION                                                                      | D7                                     | D <sub>6</sub>      | D <sub>5</sub>      | D4        | D3            | D <sub>2</sub>      | D <sub>1</sub>      | D <sub>0</sub>      | CYCLES | BYTES | C AC FO F1                            |

| ADD A, = data  | (A) - (A) + data                                                                          | ACCUM  Add Immediate the specified Data to the                                   | ULAT<br>0                              | OR<br>0             | 0                   | 0         | 0             | 0                   |                     | 1                   | 2      | 2     |                                       |

|                |                                                                                           | Accumulator.                                                                     | d7                                     | d <sub>6</sub>      | d5                  | d4        | ďЗ            | 12                  | dı                  | d0                  |        | 1     |                                       |

| ADD A, Rr      | (A) · (A) + (Rr)<br>for r = 0 - 7                                                         | Add contents of designated register to the Accumulator.                          | 0                                      | 1                   | 1                   | 0         | 1             |                     | '                   | ١.                  | 1      | '     | •                                     |

| ADD A, @ Rr    | (A) · (A) + ((Rr))<br>for r = 0 1                                                         | Add indirect the contents the data memory location to the Accumulator.           | 0                                      | 1                   | 1                   | 0         | 0             | 0                   | 0                   |                     | ١      | '     | •                                     |

| ADDC A, = data | (A) · (A) + (C) + data                                                                    | Add Immediate with carry the specified data to the Accumulator.                  | 0<br>d7                                | 0<br>d6             | 0<br>d5             | 1<br>d4   | 0<br>d3       | 0<br>d2             | 1<br>dj             | 1<br>d0             | ?      | 2     | •                                     |

| ADDC A, Rr     | (A) · (A) + (C) + (Rr)<br>for r = 0 7                                                     | Add with carry the contents of the designated register to the Accumulator.       | 0                                      | 1                   | 1                   | 1         | 1             | 1                   | ,                   | 1                   | 1      | ١ ١   | •                                     |

| ADDC A, @ Rr   | (A) - (A) + (C) + ((Rr))<br>for r = 0 1                                                   | Add Indirect with carry the contents of data memory location to the Accumulator. | 0                                      | 1                   | 1                   | 1         | 0             | 0                   | 0                   | •                   | 1      | 1     | •                                     |

| ANL A, = data  | (A) · (A) AND data                                                                        | Logical and specified Immediate Data with Accumulator.                           | 0<br>d7                                | 1<br>d <sub>6</sub> | 0<br>d5             | 1<br>d4   | 0<br>d3       | 0<br>d2             | 1<br>d <sub>1</sub> | 1<br>d <sub>0</sub> | 2      | 2     |                                       |

| ANL A, Rr      | (A) - (A) AND (Rr)<br>for r = 0 7                                                         | Logical and contents of designated register with Accumulator.                    | 0                                      | 1                   | 0                   | 1         | 1             | r                   | r                   | r                   | 1      | ١     |                                       |

| ANL A, @ Rr    | (A) · (A) AND ((Rr))<br>for r = 0 1                                                       | Logical and Indirect the contents of data memory with Accumulator.               | 0                                      | 1                   | 0                   | 1         | 0             | 0                   | 0                   | r                   | 1      | 1     |                                       |

| CPL A          | (A) - NOT (A)                                                                             | Complement the contents of the Accumulator.                                      | 0                                      | 0                   | 1                   | 1         | 0             | 1                   | 1                   | 1                   | 1      | 1     |                                       |

| CLR A          | (A) · 0                                                                                   | CLEAR the contents of the Accumulator.                                           | 0                                      | 0                   | 1                   | 0         | 0             | 1                   | 1                   | 1                   | 1      | 1     |                                       |

| DAA            |                                                                                           | DECIMAL ADJUST the contents of the Accumulator.                                  | 0                                      | 1                   | 0                   | 1         | 0             | 1                   | 1                   | 1                   | 1      | 1     | •                                     |

| DEC A          | (A) - (A) 1                                                                               | DECREMENT by 1 the accumulator's contents.                                       | 0                                      | 0                   | 0                   | 0         | 0             | 1                   | 1                   | 1                   | 1      | 1     |                                       |

| INC A          | (A) · (A) + 1                                                                             | Increment by 1 the accumulator's contents.                                       | 0                                      | 0                   | 0                   | 1         | 0             | 1                   | 1                   | 1                   | 1      | 1     |                                       |

| ORL A, = data  | (A) - (A) OR data                                                                         | Logical OR specified immediate data with Accumulator                             | 0<br>d7                                | 1<br>d <sub>6</sub> | 0<br>d5             | 0<br>d4   | 0<br>d3       | 0<br>d2             | 1<br>d1             | 1<br>d0             | 2      | 2     |                                       |

| ORL A, Rr      | (A) · (A) OR (Rr)<br>for r = 0 7                                                          | Logical OR contents of designated register with Accumulator.                     | 0                                      | !                   | 0                   | 0         | 1             | r                   | r                   | r                   | 1      | 1     |                                       |

| ORL A, @ Rr    | (A) · (A) OR ((Rr))<br>for r = 0 1                                                        | Logical OR Indirect the contents of data memory location with Accumulator.       | 0                                      | 1                   | 0                   | 0         | 0             | 0                   | 0                   | r                   | 1      | 1     |                                       |

| RLA            | $(AN + 1) \cdot (AN)$<br>$(A_0) \leftarrow (A_7)$                                         | Rotate Accumulator left by 1-bit without carry.                                  | 1                                      | 1                   | 1                   | 0         | 0             | 1                   | 1                   | 1                   | 1      | 1     |                                       |

| RLC A          | for N = 0 - 6<br>(AN + 1) (AN); N = 0 6<br>(A <sub>0</sub> ) (C)<br>(C) (A <sub>7</sub> ) | Rotate Accumulator left by 1-bit through carry.                                  | 1                                      | 1                   | 1                   | 1         | 0             | 1                   | 1                   | 1                   | 1      | 1     | •                                     |

| RR A           | (AN) (AN + 1); N = 0 - 6<br>(A <sub>7</sub> ) (A <sub>0</sub> )                           | Rotate Accumulator right by 1-bit without carry.                                 | 0                                      | 1                   | 1                   | 1         | 0             | 1                   | 1                   | 1                   | 1      | ١     |                                       |

| RRC A          | (AN) - (AN + 1); N = 0 - 6<br>(A <sub>7</sub> ) - (C)<br>(C) - (A <sub>0</sub> )          | Rotate Accumulator right by 1-bit through carry.                                 | o                                      | 1                   | 1                   | 0         | 0             | 1                   | 1                   | 1                   | 1      | 1     | •                                     |

| SWAP A         | (A <sub>4-7</sub> ) . (A <sub>0</sub> 3)                                                  | Swap the 2 4-bit nibbles in the Accumulator.                                     | Ó                                      | 1                   | 0                   | 0         | 0             | 1                   | 1                   | 1                   | 1      | '     |                                       |

| XRL A, = data  | (A) · (A) XOR data                                                                        | Logical XOR specified immediate data with Accumulator.                           | 1<br>d7                                | 1<br>d6             | 0<br>d5             | - 1<br>d4 | 0<br>d3       | 0<br>d2             | 1<br>d1             | 1<br>d0             | 2      | 2     |                                       |

| XRL A, Rr      | (A) · (A) XOR (Rr)<br>for r = 0 7                                                         | Logical XOR contents of designated register with Accumulator.                    | 1                                      | 1                   | 0                   | 1         | 1             | r,                  | r                   | r                   | 1      | 1     |                                       |

| XRL A, @ Rr    | (A) · (A) XOR ((Rr))<br>for r = 0 - 1                                                     | Logical XOR Indirect the contents of data memory location with Accumulator       | 1                                      | 1                   | 0                   | 1         | 0             | 0                   | 0                   | ,                   | 1      | ١     |                                       |

|                | ·                                                                                         | BR                                                                               | ANCH                                   |                     |                     |           |               |                     |                     |                     |        | ***** | · · · · · · · · · · · · · · · · · · · |

| DJNZ Rr, addr  | (Rr) ← (Rr) + 1; r = 0 + 7<br>If (Rr) ≠ 0.<br>(PC 0 = 7) ← addr                           | Decrement the specified register and test contents.                              | 1<br>a7                                | 1<br>36             | 1<br>a <sub>5</sub> | 0<br>a4   | 1<br>a3       | r<br>a2             | r<br>a j            | a0<br>r             | 2      | 2     |                                       |

| JBb addr       | (PC 0 - 7) addr<br>(PC 0 - 7) addr if Bb = 1<br>(PC) - (PC) + 2 if Bb = 0                 | Jump to specified address if<br>Accumulator bit is set.                          | b2                                     | b <sub>1</sub>      | b0<br>a5            | 1<br>84   | 0<br>a3       | 0<br>a2             | 1<br>81             | 0<br>a0             | 2      | 2     |                                       |

| JC addr        | (PC 0 - 7) ← addr if C = 1<br>(PC) ← (PC) + 2 if C - 0                                    | Jump to specified address if carry flag                                          | 1 27                                   | 1                   | 1<br>a <sub>5</sub> | 1 24      | 0<br>a3       | 1<br>a <sub>2</sub> | 1 81                | 90                  | 2      | 2     |                                       |

| JF0 addr       | (PC 0 7) addr if FO = 1<br>(PC) - )(PC) + 2 if FO _ 0                                     | Jump to specified address if Flag FO is set.                                     | 1 27                                   | 0<br>a6             | 1<br>a <sub>5</sub> | 1 24      | 0<br>93       | 1<br>a <sub>2</sub> | 1                   | 0<br>0              | 2      | 2     |                                       |

| JF1 addr       | (PC 0 7) + addr if F1 = 1<br>(PC) + (PC) + 2 if F1 0                                      | Jump to specified address if Flag F1 is set.                                     | 0                                      | a6<br>1<br>a6       | 45<br>1<br>85       | 1 24      | 93<br>0<br>33 | 1<br>a <sub>2</sub> | 1<br>a <sub>1</sub> | 0<br>a0             | 2      | 2     |                                       |

| JMP addr       | (PC 8 10) - addr 8 10<br>(PC 0 7) - addr 0 7<br>(PC 11) - DBF                             | Direct Jump to specified address within the 2K address block.                    | <sup>3</sup> 10                        | ag<br>a6            | a8<br>a5            | 0<br>a4   | 0<br>93       | 1<br>a2             | 0<br>a1             | 90<br>0             | 2      | 2     |                                       |

| JMPP @ A       | (PC 0 7) - ((A))                                                                          | Jump indirect to specified address with with address page                        | 1                                      | 0                   | 1                   | 1         | 0             | 0                   | 1                   | 1                   | 2      | ١,    |                                       |

| JNC addr       | (PC 0 7) + addr if C = 0<br>(PC) + (PC) + 2 if C 1                                        | Jump to specified address if garry flag is low                                   | 1<br>a7                                | 1<br>26             | 1<br>85             | 0         | 0<br>83       | 1 89                | 1<br>01             | 0<br>a0             | 2      | 2     |                                       |

| JNI addr       | (PC 0 7) - addr if 1 - 0<br>(PC) - (PC) + 2 if 1 1                                        | Jump to specified address if interrupt is low                                    | 1 87                                   | 0                   | 0<br>a5             | 0°<br>a4  | 0<br>43       | 1 12                | 1 01                | 0<br>a0             | 2      | 2     |                                       |

| L              | 1                                                                                         | L                                                                                | ــــــــــــــــــــــــــــــــــــــ | 0                   |                     | 4         | 3             |                     |                     |                     | L      | L     | L,                                    |

# INSTRUCTION SET (CONT.)

| 1 21             |                                                        | the second second second                                                    | 1       |                | INS            | TRUC    | TION C          | ODE            |                | 2              |        | l       | FL   | .AGS |   |

|------------------|--------------------------------------------------------|-----------------------------------------------------------------------------|---------|----------------|----------------|---------|-----------------|----------------|----------------|----------------|--------|---------|------|------|---|

| MNEMONIC         | FUNCTION                                               | DESCRIPTION                                                                 | D7      | D <sub>6</sub> | D <sub>5</sub> | D4      | D3              | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | CYCLES | BYTES   | C AC | FO   | 1 |

|                  |                                                        | BRAN                                                                        |         |                | - 3            |         |                 | ÷              |                | <u>`</u>       |        |         |      |      | - |

| JNT0 addr        | (PC 0 - 7) - addr if T0 = 0                            | Jump to specified address if Test 0 is low.                                 | 0       | 0              | 1              | 0       | 0               | 1              | 1              | 0              | 2      | 2       |      |      | - |

|                  | (PC) (PC) + 2 if T0 = 1                                |                                                                             | a7      | a <sub>6</sub> | a <sub>5</sub> | 84      | ag              | a2             | aı             | aO             |        | 1       |      |      |   |

| JNT1 addr        | (PC 0 7) addr if T1 0                                  | Jump to specified address if Test 1 is low.                                 | 0       | 1              | 0              | 0       | 0               | 1              | 1              | 0              | 2      | 2       |      |      |   |

|                  | (PC) · (PC) + 2 if T1 · 1<br>(PC 0 7) · addr if A + 0  |                                                                             | 97<br>1 | a6<br>0        | a5<br>0        | 94<br>1 | аз<br>О         | a2             | 91<br>1        | 0<br>a0        | 2      | 2       |      |      |   |

| JNZ addr         | (PC 0 7) - addr if A + 0<br>(PC) - (PC) + 2 if A 0     | Jump to specified address if accumulator is non-zero.                       | a7      | a6             | a <sub>5</sub> | a4      | ag              | a2             | a <sub>1</sub> | aO.            | 2      | 2       |      |      |   |

| JTF addr         | (PC 0 · 7) ← addr if TF = 1                            | Jump to specified address if Timer Flag                                     | 0       | 0              | 0              | 1       | 0               | 1              | 1              | 0              | 2      | 2       |      |      |   |

|                  | (PC) - (PC) + 2 if TF 0                                | is set to 1.                                                                | a7      | a6             | a5             | 84      | аз              | a2             | aı             | a0             |        |         |      |      |   |

| JT0 addr         | (PC 0 7) addr if T0 = 1                                | Jump to specified address if Test 0 is a .                                  | 0       | 0              | 1              | 1       | 0               | 1              | 1              | 0              | 2      | 2       |      |      |   |

| JT1 addr         | (PC) ← (PC) + 2 if T0 = 0<br>(PC 0 7) ← addr if T1 = 1 | Jump to specified address if Test 1 is a 1.                                 | a7<br>0 | a6<br>1        | a5<br>0        | a4<br>1 | а <u>з</u><br>О | a2<br>· 1      | a1<br>1        | . 0            | 2      | 2       |      |      |   |

| Jiladdr          | (PC) · (PC) + 2 · f T1 0                               | Jump to specified address if Test 1 is a 1.                                 | a7      | a <sub>6</sub> | a <sub>5</sub> | a4      | аз              | a2             | a <sub>1</sub> | a <sub>O</sub> | '      | ľ       |      |      |   |

| JZ addr          | (PC 0 - 7) - addr if A = 0                             | Jump to specified address if Accumulator                                    | 1       | 1              | 0              | 0       | 0               | 1              | . 1            | 0              | 2      | 2       |      |      |   |

|                  | (PC) · (PC) + 2 if A : 0                               | is 0.                                                                       | а7      | <sup>a</sup> 6 | a5             | 84      | аз              | <sup>8</sup> 2 | a1             | a0             |        | L       |      |      |   |

|                  |                                                        |                                                                             | ITROL   |                |                |         |                 |                |                |                |        |         |      |      |   |

| ENI              |                                                        | Enable the External Interrupt input.                                        | 0       | 0              | 0              | 0       | 0               | 1              | 0              | 1              | 1      | 1       |      |      |   |

| DISI             |                                                        | Disable the External Interrupt input.                                       | 0       | 0              | 0              | 1       | 0               | 1              | 0              | 1              | 1      | 1       |      |      |   |

| ENTO CLK         | (0.00)                                                 | Enable the Clock Output pin T0.                                             | 0       | 1              | 1              | 1       | 0               | 1              | 0              | 1              | 1 1    | 1       |      |      |   |

| SEL MBO          | (DBF) · O                                              | Select Bank 0 (locations 0 2047) of Program Memory.                         | 1       | 1              | 1              | 0       | 0 -             | 1              | 0              | 1              | 1 1    | 1       |      |      |   |

| SEL MB1          | (DBF) - 1                                              | Select Bank 1 (locations 2048 4095) of                                      | ١,      | 1              | 1              | 1       | 0               | 1              | 0              | 1              | ١,     | 1       |      |      |   |

|                  |                                                        | Program Memory.                                                             |         |                |                |         | -               |                | -              |                |        | i i     |      |      |   |

| SEL RBO          | (BS) · 0                                               | Select Bank 0 (locations 0 - 7) of Data                                     | 1       | 1              | 0              | 0       | 0               | 1              | 0              | 1              | 1      | 1       |      |      |   |

| CE1 001          | (00)                                                   | Memory.                                                                     | ١.      |                | •              | 1       | 0               |                |                |                | ١.     | ١.      |      |      |   |

| SEL RB1          | (BS) · 1                                               | Select Bank 1 (locations 24 31) of<br>Data Memory.                          | 1       | 1              | 0              | 1       | U               | 1              | 0              | 1              | 1      | 1       |      |      |   |

|                  |                                                        |                                                                             | MOV     | S              |                |         |                 |                |                |                |        |         |      |      | • |

| MOV A, = data    | (A) - data                                             | Move Immediate the specified data into                                      | 0       | 0              | 1              | 0       | 0               | 0              | 1              | 1              | 2      | 2       |      |      | • |

|                  | 1                                                      | the Accumulator.                                                            | d7      | d6             | d <sub>5</sub> | d4      | qЗ              | d2             | d <sub>1</sub> | d0             |        | 1 :     |      |      |   |

| MOV A, Rr        | (A) (Rr); r · 0 7                                      | Move the contents of the designated registers into the Accumulator.         | 1       | 1              | 1              | 1       | 1               | r              | r              | r              | 1      | 1 1     |      |      |   |

| MOV A. @ Br      | (A) - ((Rr)); r = 0 1                                  | Move Indirect the contents of data                                          | 1       | 1              | 1              | 1       | 0               | 0              | 0              | r              | 1      | 1       |      |      |   |

|                  |                                                        | memory location into the Accumulator.                                       | l '     |                | '              | •       | Ü               | Ü              | •              |                | '      | `       |      |      |   |

| MOV A, PSW       | (A) · (PSW)                                            | Move contents of the Program Status                                         | 1       | 1              | 0              | 0       | 0               | 1              | 1              | 1              | 1      | 1       |      |      |   |

|                  |                                                        | Word into the Accumulator.                                                  | 1       |                |                |         |                 |                |                |                |        | _       |      |      |   |

| MOV Rr, # data   | (Rr) data; r = 0 7                                     | Move Immediate the specified data into<br>the designated register.          | 1<br>d7 | 0<br>d6        | 1<br>d5        | 1<br>d4 | 1<br>d3         | ď2             | d <sub>1</sub> | ď <sub>0</sub> | 2      | 2       |      |      |   |

| MOV Rr. A        | (Rr) (A); r = 0 7                                      | Move Accumulator Contents into the                                          | 1       | 0              | 1              | 0       | 1               | r              | ,<br>,         | r              | 1      | 1       |      |      |   |

|                  |                                                        | designated register.                                                        | 1       | •              |                |         |                 |                |                |                | 1      |         |      |      |   |

| MOV @ Rr, A      | ((Rr)) (A); r = 0 · 1                                  | Move Indirect Accumulator Contents                                          | 1       | 0              | 1              | 0       | 0               | 0              | 0              | r              | 1      | 1       |      |      |   |

|                  |                                                        | into data memory location.                                                  | ١.      | _              |                |         | _               | _              |                |                | 1 .    |         |      |      |   |

| MOV @ Rr, ≓ data | ((Rr)) - data; r = 0 ↑                                 | Move Immediate the specified data into data memory.                         | 1<br>d7 | 0<br>d6        | 1<br>d5        | 1<br>d4 | d3              | 0<br>d2        | 0<br>d1        | ďo             | 2      | 2       |      |      |   |

| MOV PSW, A       | (PSW) · (A)                                            | Move contents of Accumulator into the                                       | 1       | 1              | o              | 1       | o               | 1              | 1              | 1              | 1      | 1       |      |      |   |

|                  |                                                        | program status word.                                                        | İ       |                |                |         |                 |                |                |                |        | l       |      |      |   |

| MOVP A, @ A      | (PC 0 7) · (A)                                         | Move data in the current page into the                                      | 1       | 0              | 1              | 0       | 0               | 0              | 1              | 1              | 2      | 1       |      |      |   |

| MOVP3 A, @ A     | (A) - ((PC))<br>(PC 0 7) - (A)                         | Accumulator.  Move Program data in Page 3 into the                          | ١,      | - 1            | 1              | 0       | 0               | 0              | 1              | 1              | 2      | ١,      |      |      |   |

| MOVIS A, & A     | (PC 8 10) - 011                                        | Accumulator.                                                                | l '     | •              | '              |         |                 | Ü              | ,              | •              | 1      | \       |      |      |   |

|                  | (A) · ((PC))                                           |                                                                             | l ·     |                |                |         |                 |                |                |                |        |         |      |      |   |

| MOVX A, @ R      | (A) ← ((Rr)); r = 0 1                                  | Move Indirect the contents of external data memory into the Accumulator.    | 1       | 0              | 0              | 0       | 0               | 0              | 0              | r              | 2      | 1.      |      |      |   |

| MOVX@R, A        | ((Rr)) - (A); r = 0 1                                  | Move Indirect the contents of the                                           | ١,      | 0              | 0              | 1       | 0               | 0              | 0              | r              | 2      | 1       |      |      |   |

|                  |                                                        | Accumulator into external data memory.                                      | ١ ٔ     | ·              | Ü              |         | •               | ·              | •              |                | _      |         |      |      |   |

| XCH A, Rr        | (A) <del>=</del> (Rr); r = 0 − 7                       | Exchange the Accumulator and                                                | 0       | 0              | 1              | 0       | 1               | r .            | r              | r              | 1      | 1       |      |      |   |

|                  |                                                        | designated register's contents.                                             | 1       |                |                |         |                 |                |                |                |        |         |      |      |   |

| XCH A, @ Rr      | (A) ∴ ((Rr)); r = 0 - 1                                | Exchange Indirect contents of Accumu-<br>lator and location in data memory. | 0       | . 0            | 1              | 0       | 0               | 0              | , 0            | r              | 1      | 1       |      |      |   |

| XCHD A. @ Rr     | (A 0 − 3) ≒ ((Rr)) 0 − 3));                            | Exchange Indirect 4-bit contents of                                         | 0       | 0              | 1              | 1       | 0               | 0              | 0              | ,              | ,      | ١,      |      |      |   |

|                  | r = 0 ~ 1                                              | Accumulator and data memory.                                                | Ľ       | _              |                |         |                 |                |                |                |        | <u></u> |      |      | _ |

|                  |                                                        | FL                                                                          | AGS     |                |                |         |                 |                |                |                |        |         |      |      | ۰ |

| CPL C            | (C) · NOT (C)                                          | Complement Content of carry bit.                                            | 1       | 0              | 1              | 0       | 0               | 1.1            | 1              | 1              | 1      | 1       | •    |      | • |

| CPL FO           | (F0) ← NOT (F0)                                        | Complement Content of Flag F0.                                              | 1       | 0              | 0              | 1       | 0               | 1              | 0              | 1              | 1      | 1       |      | •    |   |

| CPL F1           | (F1) · NOT (F1)                                        | Complement Content of Flag F1                                               | 1       | 0              | 1              | 1       | 0               | 1              | 0              | 1              | 1      | 1       |      |      |   |

| CLRC             | (C) · 0                                                | Clear content of carry bit to 0.                                            | 1       | 0              | 0              | 1       | ò               | 1              | 1              | 1              | 1      | 1       | •    |      |   |

| CLR FO           | (F0) ← 0                                               | Clear content of Flag 0 to 0.                                               | 1       | 0              | 0              | 0       | 0               | 1              | 0              | 1              | 1      | 1       |      | •    |   |

| CLR F1           | (F1) · 0                                               | Clear content of Flag 1 to 0.                                               | 1 1     | 0              | 1              | 0       | - 0             | 1              | 0              | 1              | 1 1    | 1 1     |      |      |   |

|                 |                                                                                  |                                                                       |         |                | INS     | TRUC    | TION     | ODE            |                     |         |        |             | F   | LAGS |   |

|-----------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------|----------------|---------|---------|----------|----------------|---------------------|---------|--------|-------------|-----|------|---|

| MNEMONIC        | FUNCTION -                                                                       | DESCRIPTION                                                           | D7      | D6             | D5      | D4      | D3       | D2             | D1                  | D0      | CYCLES | BYTES       | C A | C FO | F |

|                 |                                                                                  | INPUT                                                                 | OUTP    | UT             |         |         |          |                |                     |         |        |             | ,   |      |   |

| ANL BUS, = data | (BUS) - (BUS) AND data                                                           | Logical and Immediate-specified data<br>with contents of BUS.         | 1<br>d7 | 0<br>d6        | 0<br>d5 | 1<br>d4 | 1<br>d3  | 0<br>d2        | 0<br>d1             | q0<br>0 | 2      | 2           |     |      |   |

| ANL Pp, = data  | (Pp) - (Pp) AND data<br>p · 1 2                                                  | Logical and Immediate specified data<br>with designated port (1 or 2) | 1<br>d7 | 0<br>d6        | 0<br>d5 | 1<br>d4 | 1<br>d3  | 0<br>d2        | p<br>d <sub>1</sub> | p<br>do | 2      | 2           |     |      |   |

| ANLD Pp, A      | (Pp) - (Pp) AND (A 0 3)<br>p - 4 7                                               | Logical and contents of Accumulator with designated port (4 - 7).     | 1       | 0              | 0       | 1       | 1        | 1              | р                   | р       | 2      | 1           |     |      |   |

| IN A, Pp        | (A) - (Pp), p - 1 2                                                              | Input data from designated port (1 2) into Accumulator.               | 0       | 0              | 0       | 0       | 1        | 0              | р                   | р       | 2      | 1           |     |      |   |

| INS A, BUS      | (A) · (BUS)                                                                      | Input strobed BUS data into Accumulator                               | . 0     | 0              | 0       | 0       | 1        | 0              | 0                   | 0       | 2      | 1           | 1   |      |   |

| MOVD A, Pp      | (A 0 - 3) + (Pp); p = 4 7<br>(A 4 7) + 0                                         | Move contents of designated port (4 7) into Accumulator.              | 0       | 0              | 0       | 0       | 1        | 1              | р                   | ρ       | 2      | 1           |     |      |   |

| MOVD Pp, A      | (Pp) + A 0 3, p = 4 7                                                            | Move contents of Accumulator to designated port (4 – 7).              | 0       | 0              | 1       | 1       | 1        | 1              | р                   | р       | 1      | 1           |     |      |   |

| ORL BUS, = data | (BUS) · (BUS) OR data                                                            | Logical or Immediate specified data with contents of BUS.             | 1<br>d7 | .0<br>9        | 0<br>d5 | 0<br>d4 | 1<br>d3  | 0<br>d2        | 0<br>d1             | φD<br>0 | 2      | 2           |     |      |   |

| ORLD Pp. A      | (Pp) ← (Pp) OR (A 0 3)<br>p = 4 7                                                | Logical or contents of Accumulator with designated port (4 7).        | 1       | 0              | 0       | 0       | 1        | 1              | p                   | D       | 1      | 1           |     |      |   |

| ORL Pp, = data  | (Pp) + (Pp) OR data<br>p = 1 2                                                   | Logical or Immediate specified data with designated port (1 2)        | 1<br>d7 | 0<br>d6        | 0<br>d5 | 0<br>d4 | 1<br>d3  | 0<br>d2        | p<br>dj             | d<br>Ob | 2      | 2           |     |      |   |

| OUTL BUS, A     | (BUS) · (A)                                                                      | Output contents of Accumulator onto BUS.                              | 0       | 0              | 0       |         | - 0      | 0              | 1                   | e       | 1      | 1           |     |      |   |

| OUTL Pp, A      | (Pp) - (A), p = 1 2                                                              | Output contents of Accumulator to designated port (1 2).              | 0       | 0              | 1       | 1       | 1        | О              | ρ                   | р       | , 1    | 1           |     |      |   |

|                 | <u> </u>                                                                         |                                                                       | STER    | 3              |         |         |          |                |                     |         |        | <u> </u>    |     |      |   |

| DEC Rr (Rr)     | (Rr) (Rr) 1; r = 0 7                                                             | Decrement by 1 contents of designated register.                       | 1       | 1              | 0       | 0       | 1        | ſ              | r                   | 1       | 1      | 1           | Г   |      |   |

| INC Rr          | (Rr) ← (Rr) +1, r = 0 7                                                          | Increment by 1 contents of designated register.                       | 0       | 0              | 0       | 1       | 1        | r              | r                   | r       | 1      | 1           |     |      |   |

| INC @ Rr        | ((Rr)) · ((Rr)) + 1,<br>r = 0 1                                                  | Increment Indirect by 1 the contents of data memory location.         | 0       | 0              | 0       | 1       | 0        | 0              | 0                   | •       | 1      | 1           |     |      |   |

|                 | <u> </u>                                                                         | SUBR                                                                  | DUTIN   | Ε              |         | ,       |          |                |                     |         |        |             | -   |      |   |

| CALL addr       | ((SP)) · (PC), (PSW 4 7)                                                         | Call designated Subroutine.                                           | a10     | ag             | ag      | 1       | 0        | 1              | 0                   | 0       | 2      | 2           |     |      |   |

|                 | (SP) - (SP) + 1<br>(PC 8 10) - addr 8 10<br>(PC 0 - 7) addr 0 7<br>(PC 11) - DBF |                                                                       | а7      | <sup>a</sup> 6 | a5      | a4      | аз       | <sup>a</sup> 2 | aŋ                  | a0      |        |             |     |      |   |

| RET             | (SP) - (SP) 1<br>(PC) - ((SP))                                                   | Return from Subroutine without restoring Program Status Word.         | 1       | o              | 0       | 0       | 0        | 0              | 1                   | 1       | 2      | 1           |     |      |   |

| RETR            | (SP) · (SP) 1<br>(PC) · ((SP))<br>(PSW 4 7) · ((SP))                             | Return from Subroutine restoring<br>Program Status Word.              | 1       | 0              | 0       | 1       | 0        | 0              | 1                   | 1       | 2      | 1           |     |      |   |

|                 | <u> </u>                                                                         | TIMER/                                                                | COUN    | ren            |         |         |          |                |                     |         |        |             |     |      | - |

| EN TCNTI        |                                                                                  | Enable Internal interrupt Flag for<br>Timer/Counter output.           | 0       | 0              | 1       | 0       | 0        | 1              | 0                   | 1       | 1      | 1           |     |      |   |

| DIS TONTI       |                                                                                  | Disable Internal interrupt Flag for<br>Timer/Counter output.          | 0       | 0              | 1       | 1       | 0        | 1              | 0                   | 1       | 1      | 1           |     |      |   |

| MOV A, T        | (A) · (T)                                                                        | Move contents of Timer/Counter into Accumulator.                      | ō       | 1              | 0       | 0       | 0        | 0              | 1                   | 0       | 1      | 1           |     |      |   |

| MOV T, A        | (T) · (A)                                                                        | Move contents of Accumulator into<br>Timer/Counter.                   | 0       | 1              | 1       | 0       | 0        | 0              | 1                   | 0       | 1      | 1           |     |      |   |

| STOP TONT       |                                                                                  | Stop Count for Event Counter                                          | 0       | 1              | 1       | 0       | 0        | 1              | 0                   | 1       | 1      | 1           |     |      |   |

| STRT CNT        |                                                                                  | Start Count for Event Counter.                                        | 0       | 1              | 0       | 0       | 0        | 1              | 0                   | 1       | 1      | 1           |     |      |   |

| STRTT           |                                                                                  | Start Count for Timer                                                 | 0       | 1              | 0       | 1       | 0        | 1              | 0                   | 1       | 1      | 1           | ĺ   |      |   |

|                 | L                                                                                | MISCEL                                                                | -       | ous            |         |         | <u> </u> | <u> </u>       |                     |         |        | <del></del> |     |      |   |

|                 |                                                                                  | occu                                                                  |         |                |         |         |          |                |                     |         |        |             |     |      | _ |

- Notes: ① Instruction Code Designations r and p form the binary representation of the Registers and Ports involved

- The dot under the appropriate flag bit indicates that its content is subject to change by the instruction it appears in References to the address and data are specified in bytes 2 and/or 1 of the instruction.

- 4 Numerical Subscripts appearing in the FUNCTION column reference the specific bits affected.

### Symbol Definitions:

| SYMBOL                          | DESCRIPTION                      |

|---------------------------------|----------------------------------|

| Α                               | The Accumulator                  |

| AC                              | The Auxiliary Carry Flag         |

| addr                            | Program Memory Address (12 bits) |

| Bb                              | Bit Designator (b = $0-7$ )      |

| BS                              | The Bank Switch                  |

| BUS                             | The BUS Port                     |

| С                               | Carry Flag                       |

| CLK                             | Clock Signal                     |

| CNT                             | Event Counter                    |

| D                               | Nibble Designator (4 bits)       |

| data                            | Number or Expression (8 bits)    |

| DBF                             | Memory Bank Flip-Flop            |

| F <sub>0</sub> , F <sub>1</sub> | Flags 0, 1                       |

|                                 | Interrupt:                       |

| Р                               | "In-Page" Operation Designator   |

| SYMBOL                          | DESCRIPTION                                                                     |

|---------------------------------|---------------------------------------------------------------------------------|

| Pp                              | Port Designator (p = 1, 2 or 4 - 7)                                             |

| PSW                             | Program Status Word                                                             |

| Rr                              | Register Designator (r = 0, 1 or 0 7)                                           |

| SP                              | Stack Pointer                                                                   |

| T                               | Timer                                                                           |

| TF                              | Timer Flag                                                                      |

| T <sub>0</sub> , T <sub>1</sub> | Testable Flags 0, 1                                                             |

| X                               | External RAM                                                                    |

| =                               | Prefix for Immediate Data                                                       |

| @                               | Prefix for Indirect Address                                                     |

| S                               | Program Counter's Current Value                                                 |

| (x)                             | Contents of External RAM Location                                               |

| ((x))                           | Contents of Memory Location Addressed by the Contents of External RAM Location. |

| -                               | Replaced By                                                                     |

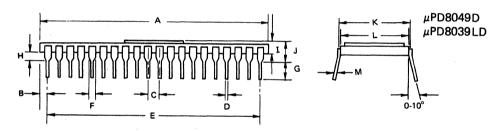

## μPD8049/8039L

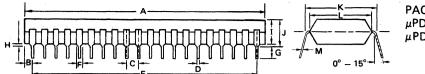

PACKAGE OUTLINES  $\mu$ PD8049C  $\mu$ PD8039LC

### (PLASTIC)

| ITEM | MILLIMETERS                   | INCHES                            |

|------|-------------------------------|-----------------------------------|

| Α    | 51.5 MAX.                     | 2.028 MAX.                        |

| В    | 1.62 MAX.                     | 0.064 MAX.                        |

| С    | 2.54 ± 0.1                    | 0.10 ± 0.004                      |

| D    | 0.5 ± 0.1                     | 0.019 ± 0.004                     |

| E    | 48.26 ± 0.1                   | 1,9 ± 0.004                       |

| F    | 1.2 MIN.                      | 0.047 MIN.                        |

| G    | 2.54 MIN.                     | 0.10 MIN.                         |

| Н    | 0.5 MIN.                      | 0.019 MIN.                        |

| I    | 5.22 MAX.                     | 0.206 MAX.                        |

| J    | 5.72 MAX.                     | 0.225 MAX.                        |

| K    | 15.24 TYP.                    | 0.600 TYP.                        |

| L    | 13.2 TYP.                     | 0.520 TYP.                        |

| М    | 0.25 <sup>+0.1</sup><br>-0.05 | 0.010 <sup>+0.004</sup><br>-0.002 |

### (CERAMIC)

| ITEM | MILLIMETERS | INCHES        |

|------|-------------|---------------|

| Α    | 51.5 MAX.   | 2.03 MAX.     |

| В    | 1,62 MAX.   | 0.06 MAX.     |

| С    | 2.54 ± 0.1  | 0.1 ± 0.004   |

| D    | 0.5 ± 0.1   | 0.02 ± 0.004  |

| E    | 48.26 ± 0.1 | 1.9 ± 0.004   |

| F    | 1.02 MIN.   | 0.04 MIN.     |

| G    | 3.2 MIN.    | 0.13 MIN.     |

| Н    | 1.0 MIN.    | 0.04 MIN.     |

| I    | 3.5 MAX.    | 0.14 MAX.     |

| J    | 4,5 MAX.    | 0.18 MAX.     |

| K    | 15.24 TYP.  | 0.6 TYP.      |

| L    | 14.93 TYP.  | 0.59 TYP.     |

| M.   | 0.25 ± 0.05 | 0.01 ± 0.0019 |