# **ADVANCE INFORMATION**

Advance information is issued to advise Customers of new additions to the Plessey Semiconductors range which, nevertheless, still have 'pre-production' status. Details given may, therefore, change without notice although we would expect this performance data to be representative of 'full production' status product in most cases. Please contact your local Plessey Semiconductors Sales Office for details of current status.

# TDA9503 LINE CIRCUIT FOR TV RECEIVERS

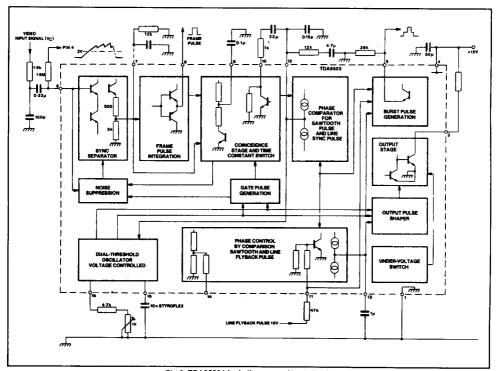

The TDA9503 is a monolithic integrated circuit for pulse separation and line synchronisation in TV receivers. The output stage of the TDA9503 (see Fig.2) supplies signals suitable for driving transistor line output stages.

An advanced version of the well-known type TBA950, the TDA9503 comprises the sync. separator with internal noise suppression, the frame pulse integrator, the phase comparator, a switching stage for automatic changeover of noise immunity and change of the slope of the phase control circuit, the line oscillator with frequency range limiter, a high-gain phase control circuit, a stage for generating the burst gate pulse in colour TV receivers, an undervoltage protection circuit and the output stage.

Due to the large scale of integration, or few external components are needed. The IC delivers prepared frame sync. pulses for triggering the frame oscillator. The phase comparator may be switched for video recording operation. A terminal (pin 14) for phase correction with the aid of the frame parabola is provided.

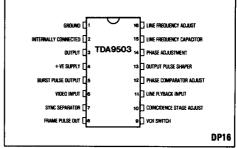

Fig.1 Pin connections (top view)

Fig.2 TDA9503 block diagram and test circuit

### TDA9503

### **ELECTRICAL CHARACTERISTICS**

# Test conditions (unless otherwise stated):

$V_4 = 12V$ ,  $f_0 = 15625$  Hz,  $T_A = 25$ °C in the test circuit Fig.2.

| Characteristic                                                                                               | Symbol                                                                | Value                 |                  |                   | Units                          | Conditions                                                                                  |  |

|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------|------------------|-------------------|--------------------------------|---------------------------------------------------------------------------------------------|--|

|                                                                                                              | Symbol                                                                | Min.                  | Тур.             | Max.              | Units                          | Conditions                                                                                  |  |

| Supply voltage<br>Current consumption                                                                        | V4<br>14                                                              | 9                     | 38               | 13<br>45          | V<br>mA                        | Pin 7 unloaded                                                                              |  |

| Pin 7  Amplitude of sync signal Output resistance (high level) Threshold for frame pulses occurring at Pin 8 | V <sub>7</sub><br>R <sub>A7</sub><br>V <sub>7th</sub>                 | 9                     | -<br>500<br>2    | -<br>-            | ν<br>Ω<br>ν                    |                                                                                             |  |

| Pin 8                                                                                                        |                                                                       |                       |                  |                   |                                |                                                                                             |  |

| Amplitude of the frame sync pulses Output resistance Frame pulse duration                                    | V <sub>s</sub><br>R <sub>A8</sub><br>t <sub>s</sub><br>t <sub>s</sub> | 10<br>—<br>150<br>300 | 1 1 1            | 100<br>350<br>650 | > Ω<br>μs<br>μs                | I <sub>a</sub> =±2mA<br>Pin 7 unloaded<br>Pin 7 connected<br>to ground via<br>1.2kΩ//0.33μF |  |

| Delay between leading edge of frame sync pulse<br>at Pin 6 and output signal at Pin 8                        | t <sub>vs</sub><br>t <sub>vs</sub>                                    | =                     | 11<br>40         | -                 | μS<br>μS                       | Pin 7 unloaded<br>Pin 7 connected<br>to ground via<br>$1.2k\Omega l/0.33\mu F$              |  |

| Pins 2 and 3                                                                                                 |                                                                       |                       |                  |                   |                                |                                                                                             |  |

| Output transistor saturation voltage                                                                         | V <sub>3/1</sub>                                                      | -                     |                  | 0.5               | V                              | 220Ω from Pin 3<br>to + 12 V                                                                |  |

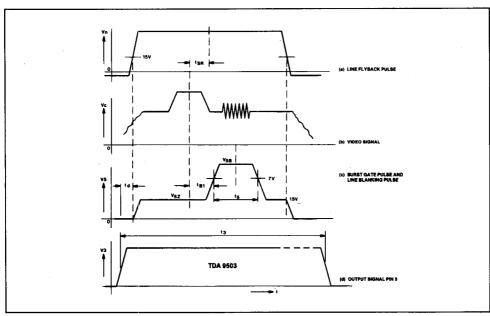

| Output pulse duration                                                                                        | t,                                                                    | 23.5                  | 26               | 28.5              | μs                             | See Fig.3                                                                                   |  |

| Pin 5                                                                                                        |                                                                       | ł                     |                  | Į.                | ·                              |                                                                                             |  |

| Burst gate pulse amplitude<br>Phase shift between centre of sync pulse and                                   | V <sub>5B</sub>                                                       | 10                    | -                | -                 | V                              | See Fig.3                                                                                   |  |

| leading edge of burst gate pulse<br>Burst gate pulse duration<br>Line blanking pulse amplitude               | t <sub>B1</sub><br>t <sub>s</sub><br>V <sub>5Z</sub>                  | 2.15<br>3.7<br>4      | 2.65<br>4<br>4.5 | 3.15<br>4.3<br>5  | μs<br>μs<br>V                  | See Fig.3                                                                                   |  |

| Oscillator frequency                                                                                         | fo                                                                    | 15625 ± 800           |                  | Hz                | C15/1 = 10nF,<br>R16/1 = 5.1kΩ |                                                                                             |  |

| Frequency pull-in and holding range<br>Slope of phase control loop                                           | ±Δf<br>t <sub>o</sub>                                                 | 650<br>100            | =                | 1200<br>—         | Hz<br>—                        |                                                                                             |  |

| Slope of the phase comparator loop                                                                           | t <sub>SR</sub>                                                       | -                     | 2                | -                 | kHz/μs                         |                                                                                             |  |

| Phase shift between sync pulse of the video signal and the line flyback pulse                                | t <sub>SR</sub>                                                       | 2.1                   | 2.6              | 3.1               | μs                             | $t_d = 5\mu s$ (see Fig.3)                                                                  |  |

### RECOMMENDED OPERATING CONDITIONS

|                                                        | Symbol          | Min. | Тур. | Max. | Unit             |

|--------------------------------------------------------|-----------------|------|------|------|------------------|

| Supply voltage                                         | V4              |      | 12   | _    | ٧                |

| Input current during sync pulse                        | 1.              | 15   | _    | 100  | μА               |

| Video signal input                                     | V.6.            | 1    | 3    | 6    | V <sub>p-p</sub> |

| input switching current for internal noise suppression | l <sub>6s</sub> | 0.5  | -    | -    | mA               |

| Input current during line flyback pulse                | l <sub>n</sub>  | 0.1  | -    | 2    | mA               |

| Switching current for VCR operation                    | ] I.            | 2    |      | -    | mA               |

| Input current (e.g. for frame parabola)                | 1,4             | -50  | _    | 50   | μΑ               |

| Ambient operating temp. range                          | TA              | 0    | ۱ –  | 60   | ა ა              |

#### **OPERATING NOTES**

The sync separator separates the synchronising pulses from the composite colour video signal. The noise inverter circuit, which needs no external components, and an internal gate circuit free the sync signal from distortion.

The frame sync pulse is obtained by internal integration and limitation of the sync signal, and is available at pin 8. The typical delay time between the leading edge of the frame sync pulses at pin 6 and the output signal at pin 8 amounts to 11 µs. This time can be enlarged by means of an external RC combination connected to pin 7, which integrates the separated frame sync pulses, before they are given to the input of the following threshold switch. The latter has a threshold of 2V.

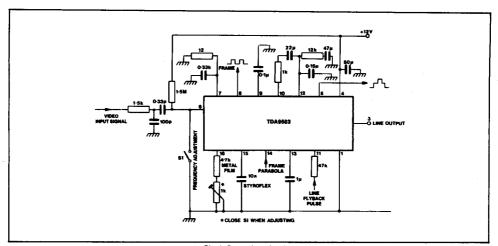

The frequency of the line oscillator is determined by a 10nF Styroflex capacitor at pin 15 which is charged and discharged periodically by two internal current sources. The external resistor at pin 16 defines the charging current and consequently in conjunction with the oscillator capacitor the line frequency.

The phase comparator compares the sawtooth voltage of the oscillator with the line sync pulse. Simultaneously an AFC voltage is generated which influences the oscillator frequency. A frequency range limiter restricts the frequency holding range.

The oscillator sawtooth voltage, which is in a fixed ratio to the line sync pulses, is compared with the line flyback pulse in the phase control circuit, in this way compensating all drift of delay times in driver and line output stage. The normal phase position is obtained if pin 14 is opencircuit. Any phase displacement can be corrected by a current or voltage fed into pin 14. The duration of the output pulse is thereby not influenced.

The burst gate pulse is derived from the sawtooth volt-

age of the line oscillator and therefore via the phase comparator synchronised with the line sync pulses of the colour video signal.

The switching stage has different functions. When the two signals supplied by the sync separator and the phase control circuit respectively are in synchronism a saturated transistor is in parallel with the integrated  $2k\Omega$  resistor at pin 10. Thus the time constant of the filter network at pin 12 increases and consequently reduces the pull-in range of the phase comparator circuit for the synchronised state. This arrangement ensures distrubance-free operation. Moreover, because the internal noise suppression and the internal gate circuit in synchronised operation are effective, the noise limitation is improved.

For video recording operation the automatic switchover can be blocked by a positive current fed into pin 9, e.g. via a resistor connected to pin 4. This reduces the time constant at pin 12 and increases the control current of the phase comparator thus steepening the static slope of the phase comparator which gives optimised matching in video recording operation.

The output transistor of the TDA9503 is operated in common emitter configuration. Its output current is limited to 50mA by the pull-up resistor between pin 3 and the supply voltage. This current serves for driving the line deflection driver transistor.

If the supply voltage goes down (e.g. by switching off the mains) a built-in protection circuit ensures defined line frequency pulses down to  $V_4$ = 4V and shuts off when  $V_4$  falls below 4V, thus preventing pulses of undefined duration and frequency. Conversely, if the supply voltage rises, pulses defined in duration and frequency will appear at the output pin as soon as  $V_4$  reaches 4.5V. In the range between  $V_4$ = 4.5V and full supply voltage the shape and frequency of the output pulses are practically constant.

Fig.3 Phase relations

Fig.4 Operating circuit

# **ABSOLUTE MAXIMUM RATINGS**

|                             | Symbol                                            | Value           | Unit           |

|-----------------------------|---------------------------------------------------|-----------------|----------------|

| Supply voltage              | V <sub>4</sub>                                    | 14              | ٧              |

| Input voltage               | V.                                                | -6              | V              |

| Output voltages             | ٧,                                                | 20              | V              |

| Output currents             | <sub>6</sub><br>±  <sub>8</sub><br>  <sub>3</sub> | -20<br>20<br>50 | mA<br>mA<br>mA |

| Input currents              | I,,<br>I₃                                         | 5<br>5          | mA<br>mA       |

| Operating temperature range | T <sub>A</sub>                                    | -10 to +60      | <b>°</b> ℃     |

| Storage temperature range   | T <sub>s</sub> '                                  | -55 to +125     | <b>°</b> C     |