## **QUAD 2-INPUT MULTIPLEXER**

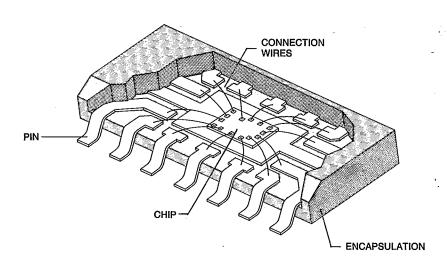

#### DESCRIPTION

The TTL/MSI T54LS158/T74LS158 is a high speed Quad 2-Input Multiplexer. It selects four bits of data from two sources using common Select and Enable inputs. The four buffered outputs present the selected data in the true inverted from. The LS158 can also generate any four of the 16 different functions of two variables. The LS158 is fabricated with the Schottky barrier diode process for high speed and is completely compatible with all SGS TTL families.

- SCHOTTKY PROCESS FOR HIGH SPEED

- MULTIFUNCTION CAPABILITY

- INVERTING OUTPUTS

- INPUT CLAMP DIODES LIMIT HIGH SPEED TERMINATION EFFECTS

- FULLY TTL AND CMOS COMPATIBLE

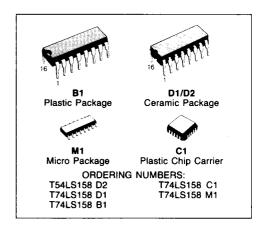

# PIN CONNECTION (top view) **DUAL IN LINE** 1 ٧<sub>cc</sub> 16 2 Ē 15 [3 14 13 12 11 GNO Z۵ PF\_nnas CHIP CARRIER ᆂᇧᅜᇰ NC = No Internal Connection

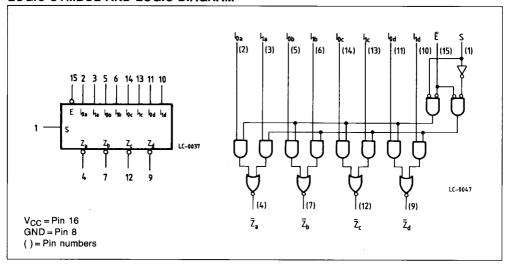

### **PIN NAMES**

| s                                | Common Select Input       |

|----------------------------------|---------------------------|

| Ē                                | Enable (Active LOW) Input |

| loa-lod                          | Data Inputs from Source 0 |

| l <sub>1a</sub> -l <sub>1d</sub> | Data Inputs from Source 1 |

| Z <sub>a</sub> -Z <sub>d</sub>   | Inverted Outputs          |

### LOGIC SYMBOL AND LOGIC DIAGRAM

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol         | Parameter                         | Value      | Unit |  |

|----------------|-----------------------------------|------------|------|--|

| $v_{cc}$       | Supply Voltage                    | -0.5 to 7  | V    |  |

| VI             | Input Voltage, Applied to Input   | -0.5 to 15 | V    |  |

| v <sub>o</sub> | Output Voltage, Applied to Output | -0.6 to 10 | V    |  |

| l <sub>l</sub> | Input Current, Into Inputs        | -30 to 5   | mA   |  |

| lo             | Output Current, Into Outputs      | 50         | mA   |  |

Stresses in excess of those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions in excess of those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **GUARANTEED OPERATING RANGES**

| Part Numbers |        |       |        |                 |  |

|--------------|--------|-------|--------|-----------------|--|

| rait numbers | Min    | Тур   | Max    | Temperature     |  |

| T54LS158D2   | 4.5 V  | 5.0 V | 5.5 V  | -55°C to +125°C |  |

| T74LS158XX   | 4.75 V | 5.0 V | 5.25 V | 0°C to +70°C    |  |

XX = package type.

#### **FUNCTIONAL DESCRIPTION**

The LS158 is a Quad 2-Input Multiplexer fabricated with the Schottky barrier diode process for high speed. It selects four bits of data from two sources under the control of the common Select Input (S) and present the data in inverted form at the four outputs. The Enable Input ( $\overline{E}$ ) is active LOW. When  $\overline{E}$  is HIGH, all of the outputs ( $\overline{Z}$ ) are forced HIGH regardless of all other inputs.

The LS158 is the logic implementation of a 4-pole, 2-position switch, where the position of the switch is determined by the logic levels supplied to the

Select Inputs.

A common use of the LS158 is the moving of data from two groups of registers to four common output buses. The particular register from which the data comes is determined by the state of the Select Input. A less obvious use is as a function generator. The LS158 can generate four functions of two variables with one variable common. This is useful for implementing gating functions.

#### TRUTH TABLE

| ENABLE | SELECT<br>INPUT | INP            | UTS            | ОИТРИТ |  |

|--------|-----------------|----------------|----------------|--------|--|

| Ē      | S               | I <sub>0</sub> | l <sub>1</sub> | Z      |  |

| Н      | Х               | Х              | Х              | Н      |  |

| L      | L               | L              | Х              | н      |  |

| L      | L               | н              | Х              | L      |  |

| L      | н               | x              | L              | н      |  |

| L      | н               | x              | Н              | L      |  |

H = HIGH Voltage Level L = LOW Voltage Level

X = Don't Care

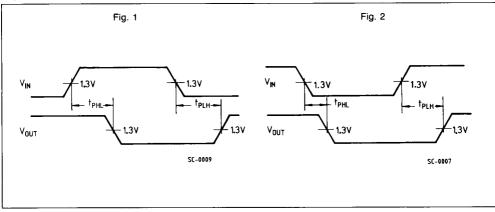

#### **AC WAVEFORMS**

# DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE

| Symbol          | Parameter  Input HIGH Voltage                                                     |       | Limits |        |                | Test Conditions                               |                                                                                                |          |

|-----------------|-----------------------------------------------------------------------------------|-------|--------|--------|----------------|-----------------------------------------------|------------------------------------------------------------------------------------------------|----------|

|                 |                                                                                   |       | Min.   | Тур.   | Max.           |                                               |                                                                                                | Units    |

| V <sub>IH</sub> |                                                                                   |       | 2.0    |        |                | Guaranteed input HIGH Voltage for all Inputs  |                                                                                                | V        |

| $V_{IL}$        | Input LOW Voltage 54                                                              |       |        |        | 0.7            | Guaranteed input LOW Voltage                  |                                                                                                | <u> </u> |

|                 |                                                                                   | 74    |        |        | 0.8            | for all Inputs                                |                                                                                                | V        |

| V <sub>CD</sub> | Input Clamp Diode Vo                                                              | Itage |        | - 0.65 | - 1.5          | V <sub>CC</sub> = MIN,I <sub>IN</sub> = -18mA |                                                                                                | v        |

| V <sub>OH</sub> | Output HIGH Voltage                                                               | 54    | 2.5    | 3.4    |                |                                               | $H = -400\mu A$ , $V_{IN} = V_{iH}$ or                                                         | v        |

|                 |                                                                                   | 74    | 2.7    | 3.4    |                | VIL per Truth                                 |                                                                                                |          |

| V <sub>OL</sub> | Output LOW Voltage                                                                | 54,74 |        | 0.25   | 0.4            | I <sub>OL</sub> = 4.0mA                       | V <sub>CC</sub> = MIN, V <sub>IN</sub> = V <sub>IH</sub> or<br>V <sub>IL</sub> per Truth Table | v        |

|                 |                                                                                   | 74    |        | 0.35   | 0.5            | I <sub>OL</sub> = 8.0mA                       |                                                                                                |          |

| liΗ             | Input HIGH Current<br>I <sub>0</sub> , I <sub>1</sub><br>E, S                     |       |        |        | 20<br>40       | V <sub>CC</sub> = MAX, V                      | / <sub>IN</sub> = 2.7V                                                                         | μА       |

|                 | Input HIGH Current at<br>Input Voltage<br>I <sub>0</sub> , I <sub>1</sub><br>E, S | Max   |        |        | 0.1<br>0.2     | V <sub>CC</sub> = MAX, V                      | / <sub>IN</sub> = 7.0V                                                                         | mA       |

| l <sub>IL</sub> | Input LOW Current I <sub>0</sub> , I <sub>1</sub> E, S                            |       | _      |        | - 0.4<br>- 0.8 | V <sub>CC</sub> = MAX, V                      | ′ <sub>IN</sub> = 0.4V                                                                         | mA       |

| los             | Output Short Circuit Current (Note 2)                                             |       | -20    |        | - 100          | V <sub>CC</sub> = MAX, V                      | OUT = 0V                                                                                       | mA       |

| lcc             | Power Supply Current                                                              |       |        | 5.0    | 8.0            | V <sub>CC</sub> = MAX                         |                                                                                                | mA       |

# AC CHARACTERISTICS: TA = 25°C

| Symbol                               | Parameter                              | Limits |          |          |        |                                                 | Units |

|--------------------------------------|----------------------------------------|--------|----------|----------|--------|-------------------------------------------------|-------|

|                                      |                                        | Min.   | Тур.     | Max.     | lest   | Test Conditions                                 |       |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay,<br>Select to Output |        | 13<br>16 | 20<br>24 | Fig. 1 |                                                 | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay,<br>Enable to Output |        | 11<br>18 | 17<br>24 | Fig. 2 | V <sub>CC</sub> = 5.0V<br>C <sub>I</sub> = 15pF | ns    |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Propagation Delay,<br>Data to Output   |        | 7<br>10  | 12<br>15 | Fig. 1 |                                                 | ns    |

#### Notes:

1) Conditions for testing, not shown in the Table, are chosen to guarantee operation under "worst case" conditions.

2) Not more than one output should be shorted at a time.

3) Typical values are at  $V_{CC} = 5.0V$ ,  $T_A = 25$  °C

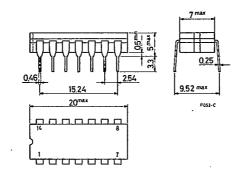

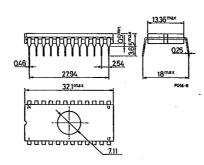

# 14-LEAD PLASTIC DIP

## 14-LEAD CERAMIC DIP

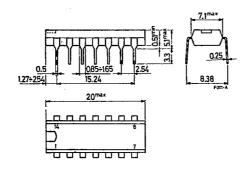

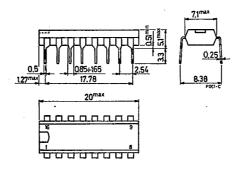

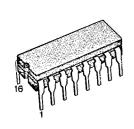

# 16-LEAD PLASTIC DIP

0606

A-13

16-LEAD CERAMIC DIP

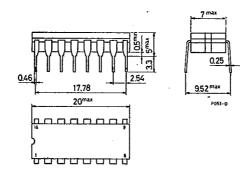

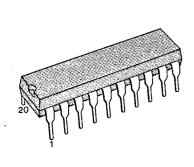

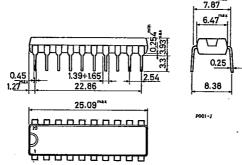

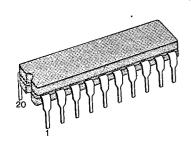

# **20-LEAD PLASTIC DIP**

# **20-LEAD CERAMIC DIP**

0607

A-14

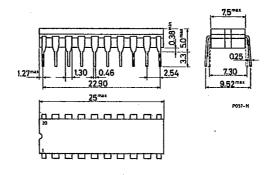

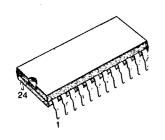

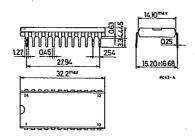

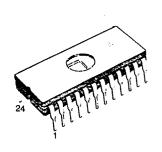

# 24-LEAD PLASTIC DIP

# 24-LEAD CERAMIC DIP

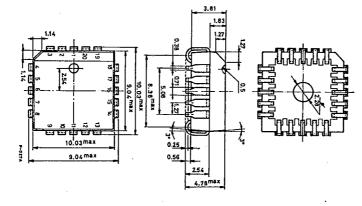

# CHIP CARRIER 20 LEAD PLASTIC

0608

B-01

NOZMOHT-Z D Z

07E D 7929237 0016418 1

**Packages**

67C 16547

D

T-90-20

14-LEAD PLASTIC DIP MICROPACKAGE

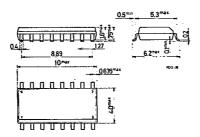

16-LEAD PLASTIC DIP MICROPACKAGE

NOTE: FOR 20-LEAD PLASTIC DIP MICROPACKAGE CONTACT SGS

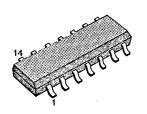

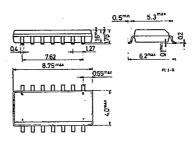

# **Surface Mounted**

67C 16548

T-90-20

One possible solution to the important problem of PWB minimization, is that of using surface mounted components. Integrated circuits in SO (Small Outline) packages are made up of standard chips mounted in very small plastic packages.

The advantages given by using these devices are:

#### **PWB Reduction**

This is by far the most important advantage since the reduction of PWB size varies from 40 to 60% in comparison with standard board types. (See page 584 for package dimensions.)

## **Assembly Cost Reduction**

SO Devices require no preliminary operation prior to mounting and can therefore be easily utilized in fully automatic equipment.

#### Increasing Reliability

The following characteristics lead to a higher level of reliability with respect to their standard packaged counter parts:

- The mounting system is fully automatic

D

- PWB number and the interconnections between them are reduced when the same number of devices are used.

- The high density of components on the board makes it thermally much more stable.

# Noise Reduction and Improved Frequency Response

The reduction of the length of the connecting wires between the leads and the silicon guarantees a more homogeneous propogation delay between the external pins, with respect to the standard type.

#### Assembly Without Board Holes

The devices are placed on the board and soldered. This technology permits a higher level of tolerance in the positioning (automatic) of the device. For the standard DIP types this must be done with great accuracy due to the insertion of the leads into their holes.