# High Performance Current Mode Controller

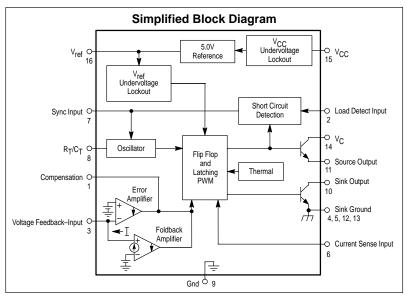

The MC44602 is an enhanced high performance fixed frequency current mode controller that is specifically designed for off-line and high voltage dc-to-dc converter applications. This device has the unique ability of changing operating modes if the converter output is overloaded or shorted, offering the designer additional protection for increased system reliability. The MC44602 has several distinguishing features when compared to conventional current mode controllers. These features consist of a foldback amplifier for overload detection, valid load and demag comparators with a fault latch for short circuit detection, thermal shutdown, and separate high current source and sink outputs that are ideally suited for driving a high voltage bipolar power transistor, such as the MJE18002, MJE18004, or MJE18006.

Standard features include an oscillator with a sync input, a temperature compensated reference, high gain error amplifier, and a current sensing comparator. Protective features consist of input and reference undervoltage lockouts each with hysteresis, cycle–by–cycle current limiting, a latch for single pulse metering, and a flip–flop which blanks the output off every other oscillator cycle, allowing output deadtimes to be programmed from 50% to 70%. This device is manufactured in a 16 pin dual–in–line heat tab package for improved thermal conduction.

- Separate High Current Source and Sink Outputs Ideally Suited for Driving Bipolar Power Transistors: 1.0 A Source, 1.5 A Sink

- Unique Overload and Short Circuit Protection

- Thermal Protection

- Oscillator with Sync Input

- Current Mode Operation to 500 kHz Output Switching Frequency

- Output Deadtime Adjustable from 50% to 70%

- Automatic Feed Forward Compensation

- Latching PWM for Cycle–By–Cycle Current Limiting

- Input and Reference Undervoltage Lockouts with Hysteresis

- Low Startup and Operating Current

# HIGH PERFORMANCE CURRENT MODE CONTROLLER

SEMICONDUCTOR TECHNICAL DATA

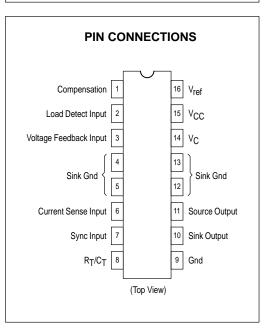

P2 SUFFIX PLASTIC PACKAGE CASE 648C DIP (12 + 2 + 2)

#### ORDERING INFORMATION

| Device  | Operating<br>Temperature Range | Package          |

|---------|--------------------------------|------------------|

| MC44602 | $T_A = -25$ to $85^{\circ}C$   | DIP (12 + 2 + 2) |

© Motorola, Inc. 1996

# MAXIMUM RATINGS

| Rating                                                                                                                                                                           | Symbol                                                   | Value           | Unit              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------|-------------------|

| Total Power Supply and Zener Current                                                                                                                                             | $(I_{CC} + I_Z)$                                         | 30              | mA                |

| Sink Ground Voltage<br>with Respect to Gnd (Pin 9)                                                                                                                               | VSink(neg)                                               | -5.0            | V                 |

| Output Supply Voltage<br>with Respect to Sink Gnd (Pins 4, 5, 12, 13)                                                                                                            | VC                                                       | 20              | V                 |

| Output Current (Note 1)<br>Source<br>Sink                                                                                                                                        | IO(Source)<br>IO(Sink)                                   | 1.0<br>1.5      | A                 |

| Output Energy (Capacitive Load per Cycle)                                                                                                                                        | W                                                        | 5.0             | μJ                |

| Current Sense and Voltage Feedback Inputs                                                                                                                                        | Vin                                                      | -0.3 to 5.5     | V                 |

| Sync Input<br>High State Voltage<br>Low State Reverse Current                                                                                                                    | VIH<br>IIL                                               | 5.5<br>-20      | V<br>mA           |

| Load Detect Input Current                                                                                                                                                        | l <sub>in</sub>                                          | -20 to +10      | mA                |

| Error Amplifier Output Sink Current                                                                                                                                              | IEA (Sink)                                               | 10              | mA                |

| Power Dissipation and Thermal Characteristics<br>Maximum Power Dissipation at $T_A = 25^{\circ}C$<br>Thermal Resistance, Junction–to–Air<br>Thermal Resistance, Junction–to–Case | Ρ <sub>D</sub><br>R <sub>θ</sub> JA<br>R <sub>θ</sub> JC | 2.5<br>80<br>15 | W<br>°C/W<br>°C/W |

| Operating Junction Temperature                                                                                                                                                   | TJ                                                       | 150             | °C                |

| Operating Ambient Temperature                                                                                                                                                    | T <sub>A</sub>                                           | -25 to +85      | °C                |

NOTE: 1. Maximum package power dissipation limits must be observed.

**ELECTRICAL CHARACTERISTICS** (V<sub>CC</sub> and V<sub>C</sub> = 12 V [Note 2], R<sub>T</sub> = 10k, C<sub>T</sub> = 1.0 nF, for typical values T<sub>A</sub> = 25°C, for min/max values T<sub>A</sub> =  $-25^{\circ}$ C to +85°C [Note 3] unless otherwise noted.)

| Characteristic                                                                                                                                                                                                                                                                             | Symbol                       | Min                   | Тур                   | Max                  | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------|-----------------------|----------------------|------|

| ERROR AMPLIFIER SECTION                                                                                                                                                                                                                                                                    |                              |                       |                       |                      |      |

| Voltage Feedback Input (V <sub>O</sub> = 2.5V)                                                                                                                                                                                                                                             | V <sub>FB</sub>              | 2.45                  | 2.5                   | 2.65                 | V    |

| Input Bias Current (V <sub>FB</sub> = 2.5 V)                                                                                                                                                                                                                                               | IIB                          | -                     | -0.6                  | -2.0                 | μΑ   |

| Open Loop Voltage Gain ( $V_0 = 2.0 \text{ V}$ to 4.0 V)                                                                                                                                                                                                                                   | Avol                         | 65                    | 90                    | -                    | dB   |

| Unity Gain Bandwidth<br>T <sub>J</sub> = 25°C<br>T <sub>A</sub> = -25 to +85°C                                                                                                                                                                                                             | BW                           | 1.0<br>0.8            | 1.4<br>-              | 1.8<br>2.0           | MHz  |

| Power Supply Rejection Ratio ( $V_{CC}$ = 10 V to 16 V)                                                                                                                                                                                                                                    | PSRR                         | 65                    | 70                    | -                    | dB   |

| Output Current<br>Sink $(V_O = 1.5 \text{ V}, V_{FB} = 2.7 \text{ V})$<br>$T_J = 25^{\circ}\text{C}$<br>$T_A = -25 \text{ to } +85^{\circ}\text{C}$<br>Source $(V_O = 5.0 \text{ V}, V_{FB} = 2.3 \text{ V})$<br>$T_J = 25^{\circ}\text{C}$<br>$T_A = -25 \text{ to } +85^{\circ}\text{C}$ | <sup>I</sup> Sink<br>ISource | -<br>1.5<br>-<br>-2.0 | 5.0<br>-<br>-1.1<br>- | -<br>10<br>-<br>-0.2 | mA   |

| Output Voltage Swing<br>High State ( $I_O(Source) = 0.5 \text{ mA}$ , VFB = 2.3 V)<br>Low State ( $I_O(Sink) = 0.33 \text{ mA}$ , VFB = 2.7 V)                                                                                                                                             | Voh<br>Vol                   | 6.0<br>-              | 7.0<br>1.0            | -<br>1.1             | V    |

NOTES: 2. Adjust V<sub>CC</sub> above the startup threshold before setting to 12V. 3. Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible.

| <b>ELECTRICAL CHARACTERISTICS</b> (V <sub>CC</sub> and V <sub>C</sub> = 12 V [Note 2], R <sub>T</sub> = 10k, C <sub>T</sub> = 1.0 nF, for typical values $T_A = 25^{\circ}$ C, for min/max |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| values $T_A = -25^{\circ}C$ to $+85^{\circ}C$ [Note 3] unless otherwise noted.)                                                                                                            |

| Characteristic                                                                                         | Symbol                   | Min         | Тур        | Max         | Unit  |

|--------------------------------------------------------------------------------------------------------|--------------------------|-------------|------------|-------------|-------|

| OSCILLATOR SECTION                                                                                     |                          |             |            |             |       |

| Frequency<br>$T_J = 25^{\circ}C$<br>$T_A = -25^{\circ}C$ to +85°C                                      | fosc                     | 168<br>160  | 180        | 192<br>200  | kHz   |

| Frequency Change with Voltage ( $V_{CC}$ = 12 V to 18 V)                                               | ΔfOSC/ΔV                 | -           | 0.1        | 0.2         | %/V   |

| Frequency Change with Temperature                                                                      | Δf <sub>OSC</sub> /ΔT    | _           | 0.05       | _           | %/°C  |

| Oscillator Voltage Swing (Peak-to-Peak)                                                                | VOSC(pp)                 | 1.3         | 1.6        | _           | V     |

| Discharge Current (V <sub>OSC</sub> = 3.0 V)<br>$T_J = 25^{\circ}C$<br>$T_A = -25^{\circ}C$ to +85°C   | ldischg                  | 6.5<br>6.0  | 10<br>-    | 13.5<br>14  | mA    |

| Sync Input Threshold Voltage<br>High State<br>Low State                                                | VIH<br>VIL               | 2.5<br>1.0  | 2.8<br>1.3 | 3.2<br>1.7  | V     |

| Sync Input Resistance<br>$T_J = 25^{\circ}C$<br>$T_A = -25^{\circ}C$ to +85°C                          | R <sub>in</sub>          | 6.5<br>6.0  | 10<br>-    | 13.5<br>18  | kΩ    |

| REFERENCE SECTION                                                                                      |                          |             |            |             |       |

| Reference Output Voltage (I <sub>O</sub> = 1.0 mA)                                                     | V <sub>ref</sub>         | 4.7         | 5.0        | 5.3         | V     |

| Line Regulation ( $V_{CC}$ = 12 V to 18 V)                                                             | Reg <sub>line</sub>      | _           | 1.0        | 10          | mV    |

| Load Regulation ( $I_O = 1.0 \text{ mA}$ to 20 mA)                                                     | Regload                  | _           | 3.0        | 15          | mV    |

| Temperature Stability                                                                                  | TS                       | _           | 0.2        | _           | mV/°C |

| Total Output Variation over Line, Load and Temperature                                                 | V <sub>ref</sub>         | 4.65        | -          | 5.35        | V     |

| Output Noise Voltage (f = 10 Hz to 10 kHz, $T_J = 25^{\circ}C$ )                                       | Vn                       | -           | 50         | -           | μV    |

| Long Term Stability (T <sub>A</sub> = 125°C for 1000 Hours)                                            | S                        | -           | 5.0        | -           | mV    |

| Output Short Circuit Current<br>$T_J = 25^{\circ}C$<br>$T_A = -25^{\circ}C$ to +85°C                   | ISC                      | _<br>_70    | -130<br>-  | _<br>_180   | mA    |

| CURRENT SENSE SECTION                                                                                  |                          |             |            |             |       |

| Current Sense Input Voltage Gain (Notes 4 & 5)<br>$T_J = 25^{\circ}C$<br>$T_A = -25^{\circ}C$ to +85°C | Av                       | 2.85<br>2.7 | 3.0        | 3.15<br>3.2 | V/V   |

| Maximum Current Sense Input Threshold (Note 4)                                                         | V <sub>th</sub>          | 0.9         | 1.0        | 1.1         | V     |

| Input Bias Current                                                                                     | IIB                      | -           | -4.0       | -10         | μΑ    |

| Propagation Delay (Current Sense Input to Sink Output)                                                 | <sup>t</sup> PLH(in/out) | -           | 100        | 150         | ns    |

| UNDERVOLTAGE LOCKOUT SECTIONS                                                                          |                          |             | •          |             | •     |

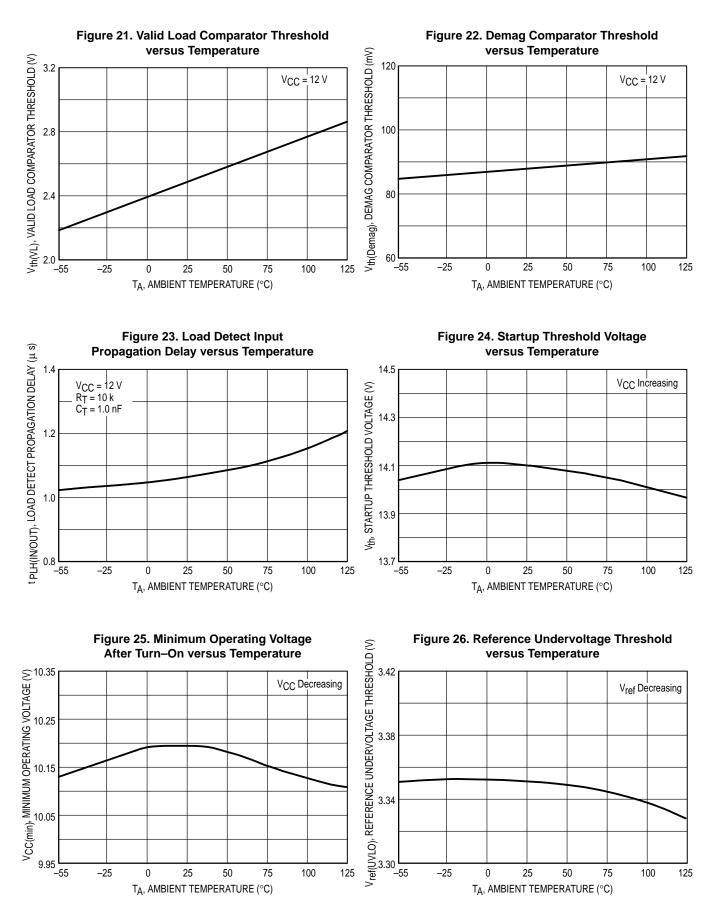

| Startup Threshold (V <sub>CC</sub> Increasing)                                                         | V <sub>th</sub>          | 13          | 14.1       | 15          | V     |

| Minimum Operating Voltage After Turn–On (V <sub>CC</sub> Decreasing)                                   | V <sub>CC(min)</sub>     | 9.0         | 10.2       | 11          | V     |

| Reference Undervoltage Threshold (Vref Decreasing)                                                     | V <sub>ref</sub> (UVLO)  | 3.0         | 3.35       | 3.7         | V     |

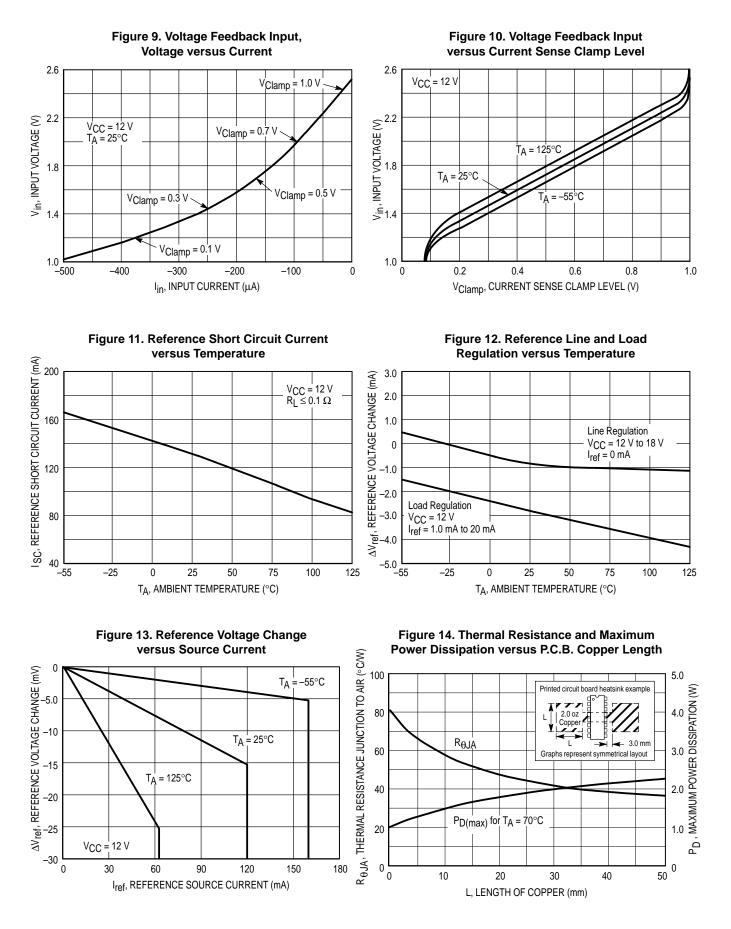

**NOTES:** 2. Adjust V<sub>CC</sub> above the startup threshold before setting to 12V. 3. Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible. 4. This parameter is measured at the latch trip point with  $I_{FB} = -5.0 \ \mu$ A, refer to Figure 9.

5. Comparator gain is defined as  $A_V = \frac{\Delta V \text{ Compensation}}{\Delta V \text{ Current Sense Input}}$

| <b>ELECTRICAL CHARACTERISTICS</b> (V <sub>CC</sub> and V <sub>C</sub> = 12 V [Note 2], $R_T$ = 10k, $C_T$ = 1.0 nF, for typical values $T_A$ = 25°C, for min/max |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| values $T_A = -25^{\circ}C$ to +85°C [Note 3] unless otherwise noted.)                                                                                           |

| Characteristic                                                                                                                                                                                       | Symbol                                                   | Min                    | Тур                    | Max                     | Unit                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------|------------------------|-------------------------|---------------------|

| OUTPUT SECTION                                                                                                                                                                                       | •                                                        |                        |                        |                         |                     |

| Output Voltage (T <sub>A</sub> = 25°C)<br>Low State (I <sub>Sink</sub> = 100 mA)<br>(I <sub>Sink</sub> = 1.0A)<br>(I <sub>Sink</sub> = 1.5 A)                                                        | VOL                                                      |                        | 0.6<br>1.8<br>2.1      | 0.3<br>2.0<br>2.6       | V                   |

| High State $(I_{Source} = 50 \text{ mA})$<br>$(I_{Source} = 0.5 \text{ A})$<br>$(I_{Source} = 0.75 \text{ A})$                                                                                       | (V <sub>CC</sub> –V <sub>OH</sub> )                      | -<br>-<br>-            | 1.4<br>1.7<br>1.8      | 1.7<br>2.0<br>2.2       |                     |

| Output Voltage with UVLO Activated (V <sub>CC</sub> = 6.0 V, $I_{Sink}$ = 1.0 mA)                                                                                                                    | VOL(UVLO)                                                | -                      | 0.1                    | 1.1                     | V                   |

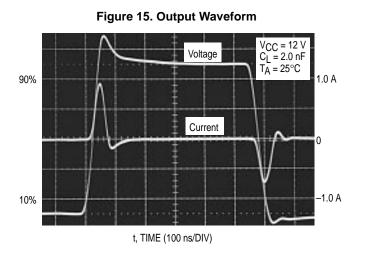

| Output Voltage Rise Time (C <sub>L</sub> = 1.0 nF, T <sub>J</sub> = $25^{\circ}$ C)                                                                                                                  | tr                                                       | -                      | 50                     | 150                     | ns                  |

| Output Voltage Fall Time ( $C_L = 1.0 \text{ nF}, T_J = 25^{\circ}C$ )                                                                                                                               | t <sub>f</sub>                                           | -                      | 50                     | 150                     | ns                  |

| PWM SECTION                                                                                                                                                                                          |                                                          |                        |                        |                         |                     |

| Duty Cycle<br>Maximum<br>Minimum                                                                                                                                                                     | DC <sub>(max)</sub><br>DC <sub>(min)</sub>               | 46<br>-                | 48<br>-                | 50<br>0                 | %                   |

| TOTAL DEVICE                                                                                                                                                                                         | •                                                        |                        |                        |                         |                     |

| Power Supply Current<br>Startup ( $V_{CC} = 5 V$ )<br>Operating (Note 2)                                                                                                                             | ICC                                                      | _                      | 0.2                    | 0.5                     | mA                  |

| $T_{J} = 25^{\circ} \text{ C}$ $T_{A} = -25^{\circ} \text{C} \text{ to } +85^{\circ} \text{ C}$                                                                                                      |                                                          | _<br>10                | 17<br>-                | 20<br>22                |                     |

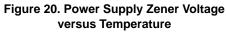

| Power Supply Zener Voltage (I <sub>CC</sub> = 25 mA)                                                                                                                                                 | VZ                                                       | 18                     | 20                     | 23                      | V                   |

| OVERLOAD AND SHORT CIRCUIT PROTECTION                                                                                                                                                                | •                                                        |                        |                        |                         |                     |

| Foldback Amplifier Threshold (Figures 9,10)                                                                                                                                                          | ΔV <sub>FB</sub>                                         | (V <sub>FB</sub> -100) | (V <sub>FB</sub> -200) | (V <sub>FB</sub> -300)  | mV                  |

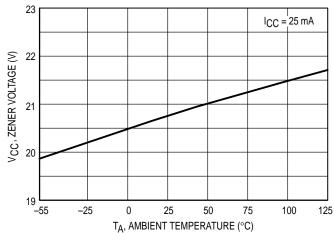

| Load Detect Input<br>Valid Load Comparator Threshold (VPin 2 Increasing)<br>Demag Comparator Threshold (VPin 2 Decreasing)<br>Propagation Delay (Input to Sink or Source Output)<br>Input Resistance | Vth(VL)<br>Vth(Demag)<br><sup>t</sup> PLH(in/out)<br>Rin | 2.0<br>50<br>-<br>12   | 2.5<br>88<br>1.1<br>18 | 3.0<br>120<br>1.6<br>30 | V<br>mV<br>μS<br>kΩ |

NOTES: 2. Adjust  $V_{\mbox{CC}}$  above the startup threshold before setting to 12V.

3. Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible.

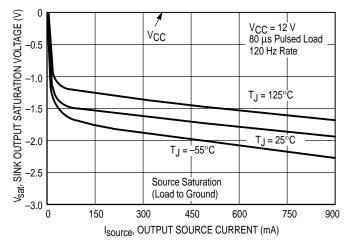

Figure 17. Sink Output Saturation Voltage versus Sink Current Vsati, SINK OUTPUT SATURATION VOLTAGE (V) TJ = −55°C Sink Saturation (Load to V<sub>CC</sub>) Tj = 25॑°C

T.j = 125°C

750

Gnd

500

250

0

32

0

0

4.0

R<sub>T</sub> = 10 k

0

Figure 18. Source Output Saturation Voltage versus Load Current

Figure 19. Supply Current versus Supply Voltage

12

V<sub>CC</sub>, SUPPLY VOLTAGE (V)

Isink, SINK OUTPUT CURRENT (mA)

1000

16

20

24

V<sub>CC</sub> = 12 V

120 Hz Rate

1250

80 µs Pulsed Load

1500

1750

8.0

#### **OPERATING DESCRIPTION**

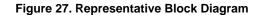

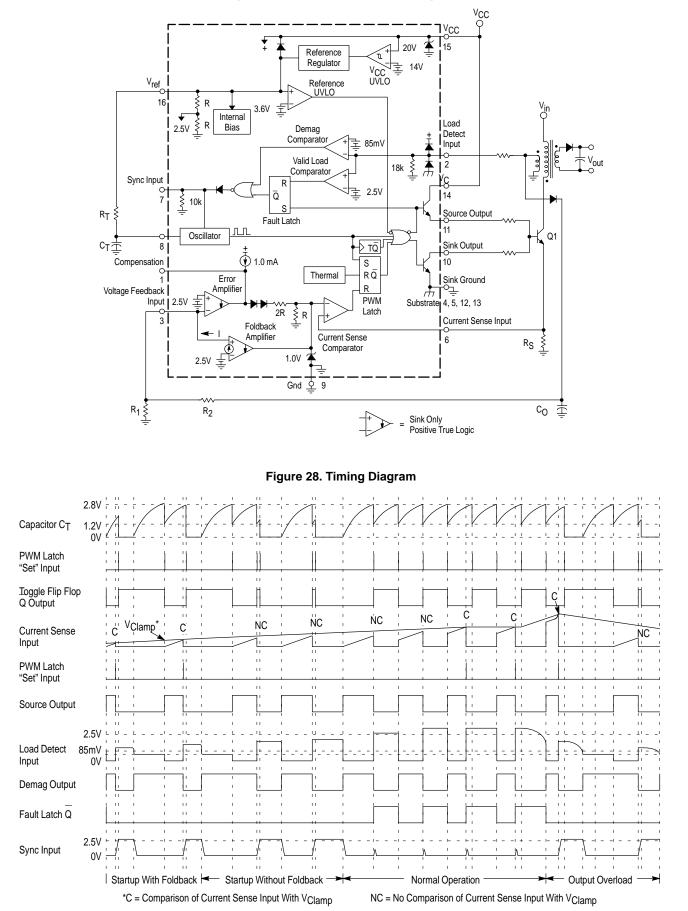

The MC44602 is a high performance, fixed frequency, current mode controller specifically designed to directly drive a bipolar power switch in off–line and high voltage dc–to–dc converter applications. This device offers the designer a cost effective solution with minimal external components. The representative block and timing diagrams are shown in Figures 27 and 28.

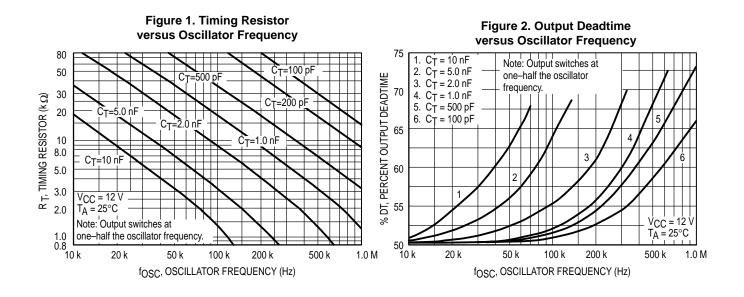

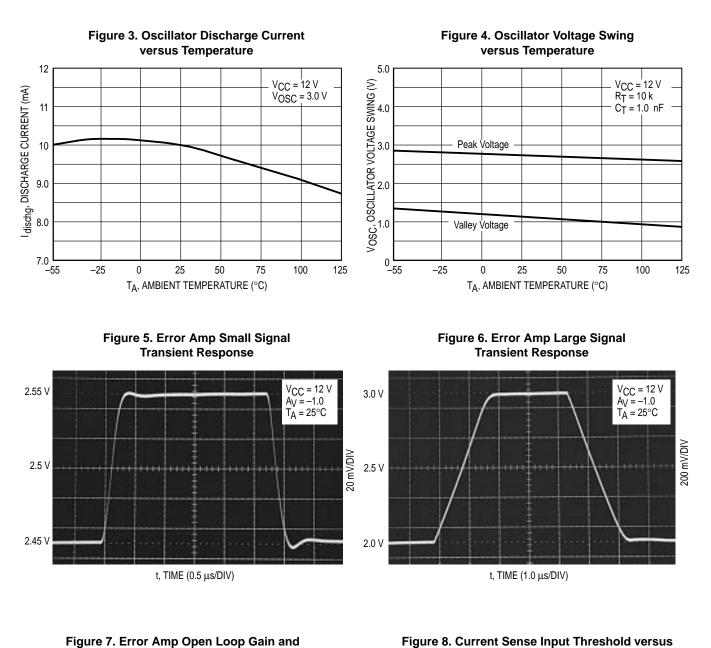

#### Oscillator

The oscillator frequency is programmed by the values selected for the timing components RT and CT. Capacitor CT is charged from the 5.0 V reference through resistor RT to approximately 2.8 V and discharged to 1.2 V by an internal current sink. During the discharge of CT, the oscillator generates an internal blanking pulse that holds one of the inputs of the NOR gate high. This causes the Source and Sink outputs to be in a low state, thus producing a controlled amount of output deadtime. An internal toggle flip-flop has been incorporated in the MC44602 which blanks the output off every other clock cycle by holding one of the inputs of the NOR gate high. This in combination with the CT discharge period yields output deadtimes programmable from 50% to 70%. Figure 1 shows RT versus Oscillator Frequency and Figure 2, Output Deadtime versus Frequency, both for a given value of CT. Note that many values of RT and CT will give the same oscillator frequency but only one combination will yield a specific output deadtime at a given frequency.

In many noise sensitive applications it may be desirable to frequency–lock the converter to an external system clock. This can be accomplished by applying a narrow rectangular clock signal with an amplitude of 3.2 V to 5.5 V to the Sync Input (Pin 7). For reliable locking, the free–running oscillator frequency should be set about 10% less than the clock frequency. If the clock signal is ac coupled through a capacitor, an external clamp diode may be required if the negative sync input current is greater than -5.0 mA. Connecting Pin 7 to V<sub>ref</sub> will cause C<sub>T</sub> to discharge to 0 V, inhibiting the Oscillator and conduction of the Source Output. Multi–unit synchronization can be accomplished by connecting the C<sub>T</sub> pin of each IC to a single MC1455 timer.

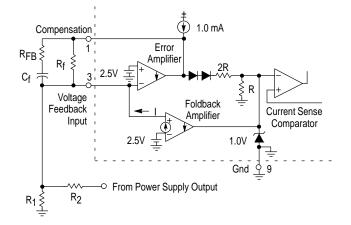

#### **Error Amplifier**

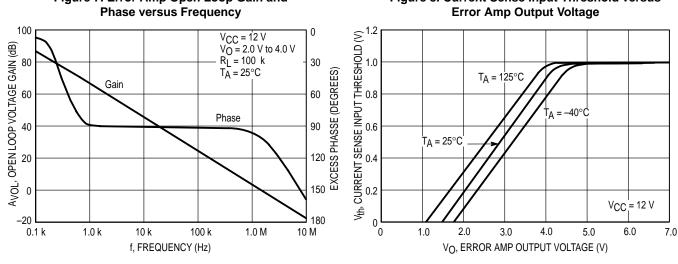

A fully compensated Error Amplifier with access to the inverting input and output is provided. It features a typical dc voltage gain of 90 dB, and a unity gain bandwith of 1.0 MHz with 57 degrees of phase margin (Figure 7). The noninverting input is internally biased at 2.5 V and is not pinned out. The converter output voltage is typically divided down and monitored by the inverting input. The maximum input bias current with the inverting input at 2.5 V is –2.0  $\mu$ A. This can cause an output voltage error that is equal to the product of the input bias current and the equivalent input divider source resistance.

The Error Amp Output (Pin 1) is provided for external loop compensation (Figure 29). The output voltage is offset by two diodes drops ( $\approx$ 1.4 V) and divided by three before it connects to the inverting input of the Current Sense Comparator. This

guarantees that no drive pulses appear at the Source Output (Pin 11) when Pin 1 is at its lowest state (V<sub>OL</sub>). This occurs when the power supply is operating and the load is removed, or at the beginning of a soft–start interval. The Error Amp minimum feedback resistance is limited by the amplifier's minimum source current (0.5 mA) and the required output voltage (V<sub>OH</sub>) to reach the comparator's 1.0 V clamp level:

$$R_{f(min)} \approx \frac{3.0 (1.0 V) + 1.4 V}{0.5 mA} = 8800 \Omega$$

#### Figure 29. Error Amplifier Compensation

#### **Current Sense Comparator and PWM Latch**

The MC44602 operates as a current mode controller, where output switch conduction is initiated by the oscillator and terminated when the peak inductor current reaches the threshold level established by the Error Amplifier output (Pin 1). Thus the error signal controls the peak inductor current on a cycle–by–cycle basis. The Current Sense Comparator PWM Latch configuration used ensures that only a single pulse appears at the Source Output during the appropriate oscillator cycle. The inductor current is converted to a voltage by inserting the ground referenced sense resistor R<sub>S</sub> in series with the emitter of output switch Q1. This voltage is monitored by the Current Sense Input (Pin 6) and compared to a level derived from the Error Amp output. The peak inductor current under normal operating conditions is controlled by the voltage at Pin 1 where:

$$I_{pk} \approx \frac{V (Pin1) - 1.4V}{3 R_S}$$

Abnormal operating conditions occur when the power supply output is overloaded or if output voltage sensing is lost. Under these conditions, the Current Sense Comparator threshold will be internally clamped to 1.0 V. Therefore the maximum peak switch current is:

$$I_{pk(max)} \approx \frac{1.0 \text{ N}}{\text{Rs}}$$

A narrow spike on the leading edge of the current waveform can usually be observed and may cause the power supply to exhibit an instability when the output is lightly loaded. This spike is due to the power transformer interwinding capacitance and the output rectifier recovery time. The addition of an RC filter on the Current Sense Input with a time constant that approximates the spike duration will usually eliminate the instability; refer to Figure 30.

#### **Undervoltage Lockout**

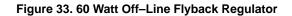

Two undervoltage lockout comparators have been incorporated to guarantee that the IC is fully functional before the output stage is enabled. The positive power supply terminal (V<sub>CC</sub>) and the reference output (V<sub>ref</sub>) are each monitored by separate comparators. Each has built–in hysteresis to prevent erratic output behavior as their respective thresholds are crossed. The V<sub>CC</sub> comparator upper and lower thresholds are 14.1 V/10.2 V. The V<sub>ref</sub> comparator upper and lower thresholds are 3.6 V/3.3 V. The large hysteresis and low startup current of the MC44602 make it ideally suited for off–line converter applications (Figures 33, 34) where efficient bootstrap startup techniques are required.

A 20 V zener is connected as a shunt regulator from V<sub>CC</sub> to ground. Its purpose is to protect the IC from excessive voltage that can occur during system startup. The upper limit for the minimum operating voltage of the MC44602 is 11V.

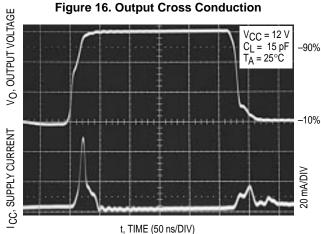

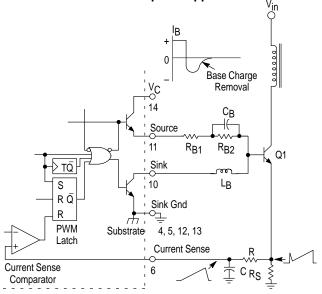

#### Outputs

The MC44602 contains a high current split totem pole output that was specifically designed for direct drive of Bipolar Power Transistors. By splitting the totem pole into separate source and sink outputs, the power supply designer has the ability to independently adjust the turn–on and turn–off base drive to the external power transistor for optimal switching. The Source and Sink outputs are capable of up to 1.0 A and 1.5 A respectively and feature 50 ns switching times with a 1.0 nF load. Additional internal circuitry has been added to keep the Source Output "Off" and the Sink Output "On" whenever an undervoltage lockout is active. This feature eliminates the need for an external pull–down resistor and guarantees that the power transistor will be held in the "Off" state.

Separate output stage power and ground pins are provided to give the designer added flexibility in tailoring the base drive circuitry for a specific application. The Source Output high–state is controlled by applying a positive voltage to V<sub>C</sub> (Pin 14) and is independent of V<sub>CC</sub>. A zener clamp is typically connected to this input when driving power MOSFETs in systems where V<sub>CC</sub> is greater than 20V. The Sink Output low–state is controlled by applying a negative voltage to the Sink Ground (Pins 4, 5, 12, 13). The Sink Ground can be biased as much as 5.0 V negative with respect to Ground (Pin 7). Proper implementation of the V<sub>C</sub> and Sink Ground pins will significantly reduce the level of switching transient noise imposed on the control circuitry.

This becomes particularly useful when reducing the lpk(max) clamp level.

#### Reference

The 5.0 V bandgap reference has a tolerance of  $\pm 6.0\%$  over a junction temperature range of  $-25^{\circ}$ C to  $85^{\circ}$ C. Its primary purpose is to supply charging current to the oscillator timing capacitor. The reference has short circuit protection and is capable of providing in excess of 20 mA for powering additional control system circuitry.

#### Figure 30. Bipolar Transistor Drive and Current Spike Suppression

#### **Thermal Protection and Package**

Internal Thermal Shutdown circuitry is provided to protect the integrated circuit in the event that the maximum junction temperature is exceeded. When activated, typically at 160°C, the PWM Latch is held in the "reset" state, forcing the Source Output "Off" and the Sink Output "On". This feature is provided to prevent catastrophic failures from accidental device overheating. It is not intended to be used as a substitute for proper heatsinking.

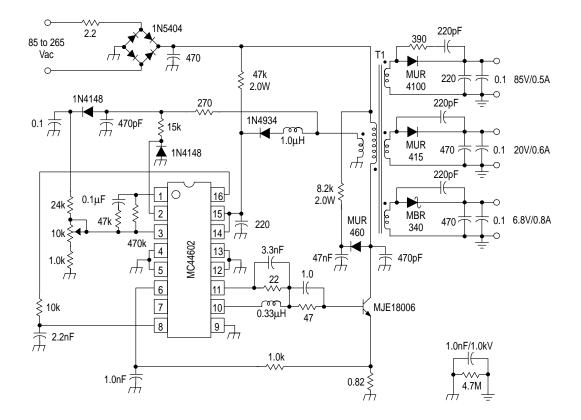

The MC44602 is contained in a heatsinkable 16–lead plastic dual–in–line package in which the die is mounted on a special heat tab copper alloy lead frame. This tab consists of the four center Sink Ground pins that are specifically designed to improve the thermal conduction from the die to the circuit board. Figure 14 shows a simple and effective method of utilizing the printed circuit medium as a heat dissipater by soldering these pins to an adequate area of copper foil. This permits the use of standard layout and mounting practices while having the ability to halve the junction to air thermal resistance. This example is for a symmetrical layout on a single–sided board with two ounce per square foot of copper.

#### **Design Considerations**

Do not attempt to construct the converter on wire-wrap or plug-in prototype boards. High frequency circuit layout techniques are imperative to prevent pulse-width jitter. This is usually caused by excessive noise pick-up imposed on the Current Sense or Voltage Feedback inputs. Noise immunity can be improved by lowering circuit impedances at these points. The printed circuit layout should contain a ground plane with low-current signal, and high current switch and output grounds returning on separate paths back to the input filter capacitor. Ceramic bypass capacitors (0.1  $\mu$ F) connected directly to V<sub>CC</sub>, V<sub>C</sub>, and V<sub>ref</sub> may be required depending upon circuit layout. This provides a low impedance path for filtering the high frequency noise. All high current loops should be kept as short as possible using heavy copper runs to minimize radiated EMI. The Error Amp compensation circuitry and the converter output voltage divider should be located close to the IC and as far as possible from the power switch and other noise generating components.

#### **PROTECTION MODES**

The MC44602 operates as a conventional fixed frequency current mode controller when the power supply output load is less than the design limit. For enhanced system reliability, this device has the unique ability of changing operating modes if the power supply output is overloaded or shorted.

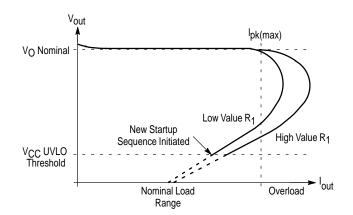

#### **Overload Protection**

Power supply overload protection is provided by the Foldback Amplifier. As the output load gradually increases, the Error Amplifier senses that the voltage at Pin 3 is less than the 2.5 V threshold. This causes the voltage at Pin 1 to rise, increasing the Current Sense Comparator threshold in order to maintain output regulation. As the load further increases, the inverting input of the Current Sense Comparator reaches the internal 1.0 V clamp level, limiting the switch current to the calculated Ipk(max). At this point any further increase in load will cause the power supply output to fall out of regulation. As the voltage at Pin 3 falls below 2.5 V, current will flow out of the Foldback Amplifier input, and the internal clamp level will be proportionally reduced (Figures 9, 10). The increase in current flowing out of the Foldback Amplifier input in conjunction with the reduced clamp level, causes the power supply output voltage to fall at a faster rate than the voltage at Pin 3. This results in the output foldback characteristic shown in Figure 31. The shape of the current limit "knee" can be modified by the value of resistor R1 in the feedback divider. Lower values of R1 will reduce the lpk(max) clamp level at a faster rate.

Improper operation of the Foldback Amp can be encountered when the Error Amp compensation capacitor Cf exceeds 2.0 nF. The problem appears at Startup when the output voltage of the power supply is below nominal, causing the Error Amp output to rise quickly. The rapid change in output voltage will be coupled through Cf to the Inverting Input (Pin 3), keeping it at its 2.5 V threshold as the 1.0 mA Error Amp current source charges Cf. This has the effect of disabling the Foldback Amp by preventing Pin 3 and the clamp level at the inverting input of the Current Sense Comparator, from rising in proportion to the power supply output voltage. By adding resistor RFB in series with Cf, the voltage at Pin 3 can be held to 1.0 V, corresponding to a Current Sense clamp level of 0.08 V (Figure 10), while allowing the Error Amp output to reach its high state VOH of 7.0 V. The required resistor to keep Pin 3 below 1.0 V during initial Startup is:

$$\frac{\mathsf{R}_{\mathsf{F}}\mathsf{B}\,\mathsf{R}_{\mathsf{f}}}{\mathsf{R}_{\mathsf{F}}\mathsf{B}+\mathsf{R}_{\mathsf{f}}} \ge 6\left(\frac{\mathsf{R}_{\mathsf{1}}\,\mathsf{R}_{\mathsf{2}}}{\mathsf{R}_{\mathsf{1}}+\mathsf{R}_{\mathsf{2}}}\right)$$

#### Figure 31. Output Foldback Characteristic

#### **Short Circuit Protection**

Short circuit protection for the power supply is provided by the Valid Load Comparator, Fault Latch, and Demag Comparator. Figure 32 shows the logic truth table of the functional blocks. When operating the power supply with nominal output loading, the Fault Latch is "Set" by the NOR gate driver during the Power Transistor "On" time and "Reset" by the Fault Comparator during the "Off" time. When a severe overload or short circuit occurs on any output, the voltage during the "Off" time (flyback voltage) at the Load Detect Input, is unable to reach the 2.5 V threshold of the Valid Load Comparator. This causes the Fault Latch to remain in the "Set" state with output Q "Low". During the "Off" time the Demag Comparator output will also be "Low". This causes the NOR gate to internally hold the Sync Input "High", inhibiting the next fixed frequency Oscillator cycle and switching of the Power Transistor. As the load dissipates the stored transformer energy, the voltage at the Load Detect Input will fall. When this voltage reaches 85 mV, the Demag Comparator output goes "High", allowing the Sync Input to go "Low", and the Power Transistor to turn "On".

Note that as long as there is an output short, the switching frequency will shift to a much lower frequency than that set by  $R_T/C_T$ . The frequency shift has the effect of lowering the duty cycle, resulting in a significant reduction in Power Transistor and Output Rectifier heating when compared to conventional current mode controllers. The extended "On" time is the result of  $C_T$  charging from 0 V to 2.8 V instead of 1.2 V to 2.8 V. The extended "Off" time is the result of the output short time constant. The time constant consists of the output filter capacitance, and the equivalent series resistance (ESR) of the capacitor plus the associated wire resistance.

| Output  | Power       | Demag          |     | Fa | ult Lat | ch | Sync  |                                                                                                              |

|---------|-------------|----------------|-----|----|---------|----|-------|--------------------------------------------------------------------------------------------------------------|

| Load    | Transistor  | Input          | Out | S  | R       | Q  | Input | Operating Comments                                                                                           |

| Nominal | On          | <85mV          | 1   | 1  | 0       | 0  | 0     | NOR gate driver sets Fault Latch.                                                                            |

|         | At Turn–Off | >85 mV, <2.5 V | 0   | 0  | 0       | 0  | _/_   | Narrow spike at Sync Input (<2.5 V) as transformer voltage rises quickly, Oscillator is not affected.        |

|         | Off         | >2.5 V         | 0   | 0  | 1       | 1  | 0     | Valid Load Comparator resets Fault Latch.                                                                    |

| Short   | On          | <85 mV         | 1   | 1  | 0       | 0  | 0     | Short is not detected until transistor turn-off.                                                             |

|         | At Turn–Off | >85 mV, <2.5 V | 0   | 0  | 0       | 0  | 1     | Valid Load Comparator fails to reset Fault Latch, Pulse at Sync Input exceeds 2.5 V, Oscillator is disabled. |

|         | Off         | <85 mV         | 1   | 0  | 0       | 0  | 0     | Load dissipates transformer energy, Oscillator enabled.                                                      |

Figure 32. Logic Truth Table of Functional Blocks

During the initial power supply startup the controller sequences through the Short Circuit and Overload Protection modes as the output filter capacitors charge-up. If an output is shorted and the auxiliary feedback winding is used to power the control IC as in Figure 33, the V<sub>CC</sub> UVLO lower threshold level will be reached after several cycles, disabling the IC and initiating a new startup sequence. The Short Circuit Protection mode can be disabled by grounding the Sync Input. Narrow switching spikes are present on this pin during normal operation. These spikes are caused by the rise time of the flyback voltage from the 85 mV Demag Comparator threshold to the 2.5 V Valid Load Comparator threshold. In high power applications, the increased negative current at the Load Detect Input can extend the switching spikes to the point where they exceed the Sync Input threshold. This problem can be eliminated by placing an external small signal clamp diode at the Load Detect Input. The diode is connected with the cathode at Pin 2 and the anode at around.

The divide–by–two toggle flip–flop will appear not to function properly during power supply startup without foldback, or operation with an overloaded output. This phenomena appears at the end of the oscillator cycle if there was not a current sense comparison, and after the flyback voltage at the Load Detect Input failed to exceed 2.5 V. Under these conditions, the Sync input will go high approximately  $1.0 \,\mu$ s after the Load Detect Input exceeds the 85 mV Demag

Comparator threshold. This causes CT to discharge down towards ground, generating a second negative going edge on the oscillator waveform. This second edge results in the divide-by-two flip-flop being clocked twice for each "On" time of the switch transistor. During initial startup, this effect can be eliminated by insuring that the Foldback Amplifier is fully active with the addition of resistor RFB. With the Foldback Amplifier active, the clamp level at the inverting input of the Current Sense Comparator will be low, allowing a comparison to take place during the switch transistor "On" time. When the Load Detect Input exceeds 85 mV, the Sync Input will go high, discharging  $C_T$  to ground after 1.0  $\mu$ s, thus eliminating the second negative edge. Operation with the output overloaded will cause the toggle flip-flop to be clocked twice for each "On" time. This should not be a problem since the next "On" time is delayed by the Demag Comparator until the load dissipates the transformers energy.

The point where the IC detects that there is a severe output overload, or that the transformer has reached zero current, is controlled by the voltage of the auxiliary winding and a resistor divider. The divider consists of an external series resistor and an internal shunt resistor. The shunt resistor is nominally 18 k $\Omega$  but can range from 12 k $\Omega$  to 30 k $\Omega$  due to process variations. If more precise overload and zero current detection is required, the internal resistor variations can be swamped out by connecting a low value external resistor ( $\leq 2.7 \text{ k}\Omega$ ) from Pin 2 to ground.

# PIN FUNCTION DESCRIPTION

| Pin          | Function                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | Compensation                   | This pin is the Error Amplifier output and is made available for loop compensation.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2            | Load Detect Input              | A voltage indicating a severe overload or short circuit condition at any output of the switching power supply is connected to this input. The Oscillator is controlled by this information making the power supply short circuit proof.                                                                                                                                                                                                                                                               |

| 3            | Voltage Feedback Input         | This is the inverting input of the Error Amplifier and the noninverting input of the Foldback Amplifier. It is normally connected to the switching power supply output through a resistor divider.                                                                                                                                                                                                                                                                                                    |

| 4, 5, 12, 13 | Sink Ground                    | The Sink Ground pins form a single power return that is typically connected back to the power source on a separate path from Pin 9 Ground, to reduce the effects of switching transient noise on the control circuitry. These pins can be used to enhance the package power capabilities (Figure 14). The Sink Output low state (V <sub>OL</sub> ) can be modified by applying a negative voltage to these pins with respect to Ground (Pin 9) to optimize turn–off of a bipolar junction transistor. |

| 6            | Current Sense Input            | A voltage proportional to inductor current is connected to this input. The PWM uses this information to terminate conduction of the output switch transistor.                                                                                                                                                                                                                                                                                                                                         |

| 7            | Sync Input                     | A narrow rectangular waveform applied to this input will synchronize the Oscillator. A dc voltage within the range of 3.2 V to 5.5 V will inhibit the Oscillator.                                                                                                                                                                                                                                                                                                                                     |

| 8            | R <sub>T</sub> /C <sub>T</sub> | The Oscillator frequency and maximum Output duty cycle are programmed at this pin by connecting resistor $R_T$ to $V_{ref}$ and capacitor $C_T$ to ground.                                                                                                                                                                                                                                                                                                                                            |

| 9            | Ground                         | This pin is the control circuitry ground and is typically connected back to the power source on a separate path from the Sink Ground (Pins 4, 5, 12, 13).                                                                                                                                                                                                                                                                                                                                             |

| 10           | Sink Output                    | Peak currents up to 1.5 A are sunk by this output suiting it ideally for turning–off a bipolar junction transistor. The output switches at one–half the oscillator frequency.                                                                                                                                                                                                                                                                                                                         |

| 11           | Source Output                  | Peak currents up to 1.0 A are sourced by this output suiting it ideally for turning–on a bipolar junction transistor. The output switches at one–half the oscillator frequency.                                                                                                                                                                                                                                                                                                                       |

| 14           | VC                             | The Output high state ( $V_{OH}$ ) is set by the voltage applied to this pin. With a separate connection to the power source, it can reduce the effects of switching transient noise on the control circuitry.                                                                                                                                                                                                                                                                                        |

| 15           | Vcc                            | This pin is the positive supply of the control IC. The minimum operating voltage range after startup is 11 V to 18 V.                                                                                                                                                                                                                                                                                                                                                                                 |

| 16           | V <sub>ref</sub>               | This is the 5.0 V reference output. It provides charging current for capacitor CT through resistor RT and can be used to bias any additional system circuitry.                                                                                                                                                                                                                                                                                                                                        |

| Test                                  | Conditions                                                                                                                                                  | Results                                                                                                                    |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Line Regulation<br>85V<br>20V<br>6.8V | $V_{in} = 85$ Vac to 265 Vac<br>$I_O = 0.5$ A<br>$I_O = 0.5$ A<br>$I_O = 0.8$ A                                                                             | $\Delta$ = 1.0 V or ± 0.6%<br>$\Delta$ = 0.04 V or ± 0.1%<br>$\Delta$ = 0.07 V or ± 0.5%                                   |

| Load Regulation<br>85V<br>20V<br>6.8V | $V_{in} = 220 \text{ Vac}$<br>$I_O = 0.1 \text{ A to } 0.5 \text{ A}$<br>$I_O = 0.1 \text{ A to } 0.5 \text{ A}$<br>$I_O = 0.1 \text{ A to } 0.8 \text{ A}$ | $\Delta = 1.0 \text{ V or } \pm 0.6\%$<br>$\Delta = 0.4 \text{ V or } \pm 1.0\%$<br>$\Delta = 0.2 \text{ V or } \pm 1.5\%$ |

| Efficiency                            | V <sub>in</sub> = 110 Vac, P <sub>O</sub> = 58 W                                                                                                            | 81%                                                                                                                        |

| Standby Power                         | V <sub>in</sub> = 110 Vac, P <sub>O</sub> = 0 W                                                                                                             | 2.0 W                                                                                                                      |

T1 - Orega SMT2 (G4787-01)

Primary: 41 Turns, #25AWG Auxiliary Feedback: 12 Turns, #25AWG

Secondary: 85 V – 60 Turns, #25AWG 20 V – 15 Turns, #25AWG (2 Strands) Bifiliar Wound

6.8 V - 5 Turns, #25AWG (2 Strands) Bifiliar Wound

Core - ETD39 34x17x11 B52

Gap  $~-~\approx 0.020''$  for a primary inductance of 750  $\mu H,~A_L$  = 500 nH/Turn^2

#### 0 ∕∕∕∿ 4.7 1N5404 220pF 390 -16 220 Vac 100 Τ1 d东 0 47k 2.0W MUR þ 220 0.1 155V/0.5A Ş 4100 С 1N4148 220pF 270 -16 0.1 ± 470pF 1N4934 ≶ 15k 20 لى الله ◀ C 00000 1.0µH **\*** MUR þ 0.1 24.5V/1.8A 470 1N4148 415 C 220pF 8.2k 2.0W ╢ 0 ≶ 1 16 0.1µF 24k ≷ C ≶ 2 15 MUR 90 15.5V/1.8A MUR 47k 0.1 470 220 415 460 10k 3 14 0 470k MC44602 4 13 3.3nF Ť 47nF 470pF 1.0k Æ -16 Æ 5 12 1.0 22 6 11 lf 7 10 00 MJE18006 2.2µH \_\_\_\_ بہر فا 47 8 2.2nF Ť 1.0nF/1.0kV 1.0k -1(- $\sim$ 1.0nF 茾 0.47 אי ה 4.7M h

# Figure 34. 150 Watt Off-Line Flyback Regulator

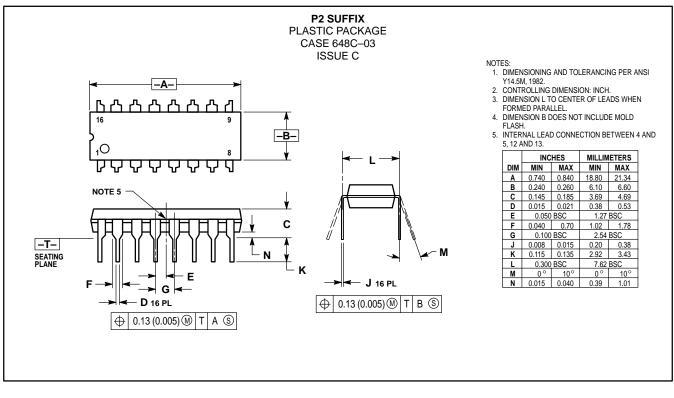

| Test                                      | Conditions                                                                                                                                                        | Results                                                                                                                    |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Line Regulation<br>155V<br>24.5V<br>15.5V | $V_{in} = 185$ Vac to 265 Vac<br>I <sub>O</sub> = 0.5 A<br>I <sub>O</sub> = 1.0. A<br>I <sub>O</sub> = 1.0 A                                                      | $\Delta = 1.0 \text{ V or } \pm 0.3\%$<br>$\Delta = 0.4 \text{ V or } \pm 0.8\%$<br>$\Delta = 0.3 \text{ V or } \pm 1.0\%$ |

| Load Regulation<br>155V<br>24.5V<br>15.5V | $V_{in} = 220 \text{ Vac}$<br>$I_{O} = 0.1 \text{ A to } 0.5 \text{ A}$<br>$I_{O} = 0.1 \text{ A to } 1.0 \text{ A}$<br>$I_{O} = 0.1 \text{ A to } 1.0 \text{ A}$ | $\Delta = 2.0 \text{ V or } \pm 0.7\%$<br>$\Delta = 0.4 \text{ V or } \pm 0.8\%$<br>$\Delta = 0.2 \text{ V or } \pm 0.7\%$ |

| Efficiency                                | V <sub>in</sub> = 220 Vac, P <sub>O</sub> = 117.5 W                                                                                                               | 83%                                                                                                                        |

| Standby Power                             | V <sub>in</sub> = 220 Vac, P <sub>O</sub> = 0 W                                                                                                                   | 5.0 W                                                                                                                      |

T1 - Orega SMT2 (G4717-01)

Primary: 55 Turns, #25AWG

Auxiliary Feedback: 6 Turns, #25AWG Secondary: 155 V – 52 Turns, #25AWG

24.5 V - 9 Turns, #25AWG (2 Strands) Bifiliar Wound 15.5 V - 6 Turns, #25AWG (2 Strands) Bifiliar Wound

Core - GETV 53x18x18 B52

Gap  $~-~\approx 0.020''$  for a primary inductance of 1.35  $\mu H,~A_L$  = 450 nH/Turn^2

## **OUTLINE DIMENSIONS**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and **O** registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447 or 602–303–5454

$\Diamond$

MFAX: RMFAX0@email.sps.mot.com – TOUCHTONE 602–244–6609 INTERNET: http://Design\_NET.com JAPAN: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 03–81–3521–8315

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298