# DUAL J-K POSITIVE EDGE-TRIGGERED FLIP FLOP WITH SET AND RESET

#### DESCRIPTION

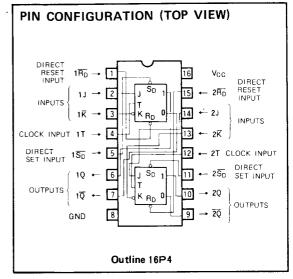

The M74LS109AP is a semiconductor integrated circuit containing 2 J- $\overline{K}$  positive edge-triggered flip-flop circuits with discrete terminals for clock input T, inputs J and  $\overline{K}$ , and direct set and reset inputs  $\overline{S_D}$  and  $\overline{R_D}$ .

#### **FEATURES**

- Positive edge-triggering

- · Each flip-flop can be used independently

- Direct set and reset inputs

- J and K inputs

- Q and Q outputs

- Wide operating temperature range (T<sub>a</sub> = −20~+75°C)

#### **APPLICATION**

General purpose, for use in industrial and consumer equipment.

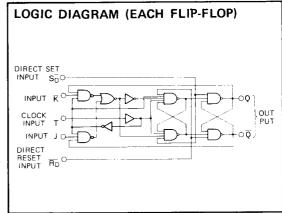

#### **FUNCTIONAL DESCRIPTION**

When T changes from low to high, the J and  $\overline{K}$  signals immediately before the change emerge in outputs Q and  $\overline{Q}$  in accordance with the function table. By using  $\overline{S_D}$  and  $\overline{R_D}$ , this IC can be made into a direct R-S flip-flop. When both  $\overline{S_D}$  and  $\overline{R_D}$  are low, Q =  $\overline{Q}$  = high. However, when both of them change to high at the same time, the status of Q and  $\overline{Q}$  cannot be anticipated. For use as a J-K flip-flop,  $\overline{S_D}$  and  $\overline{R_D}$  must be kept in high. By connecting J and  $\overline{K}$ , this IC can be used as a D-type flip-flop.

#### FUNCTION TABLE (Note 1)

| SD | RD | Т | J | Ŕ | Q              | Q              |  |

|----|----|---|---|---|----------------|----------------|--|

| L  | Н  | X | Х | × | н              | L              |  |

| H  | L  | Х | X | × | L              | н              |  |

| L  | L  | X | Х | × | н*             | н*             |  |

| Н  | н  | L | × | Х | Q <sup>0</sup> | Q <sup>0</sup> |  |

| Н  | н  | 1 | L | L | L              | н              |  |

| Н  | н  | 1 | н | L | Toggle         |                |  |

| н  | Н  | 1 | L | н | Q°             | Q <sup>0</sup> |  |

| Н  | н  | 1 | Н | н | Н              | L              |  |

- Note 1 ↑: Transition from low to high-level (positive edge trigger)

- Q<sup>0</sup>: Level of Q before the indicated steady-state input conditions were established.

- $\overline{Q^0}$ : Level of  $\overline{Q}$  before the indicated steady-state input conditions were established. Toggle: complement of previous state with 1 transition of output

- X : Irrelevant

- \*:  $Q = \overline{Q} = \text{high when } \overline{S_D} = \overline{R_D} = \text{low and so when both } \overline{S_D} \text{ and } \overline{R_D} \text{ are set high, the status of } Q \text{ and } \overline{Q} \text{ cannot be anticipated.}$

#### ABSOLUTE MAXIMUM RATINGS (Ta = +20 ~ +75℃, unless otherwise noted)

| Symbol | Parameter                                    | Conditions       | Limits                 | Unit |

|--------|----------------------------------------------|------------------|------------------------|------|

| Vcc    | Supply voltage                               |                  | -0.5~+7                | V    |

| Vı     | Input voltage                                |                  | -0.5-+5.5              | ٧    |

| Vo     | Output voltage                               | High-level state | -0.5 ~ V <sub>CC</sub> | ٧    |

| Topr   | Operating free-air ambient temperature range |                  | - 20 - + 75            | Υ .  |

| Tstg   | Storage temperature range                    |                  | -65~ + 150             | r    |

# DUAL J-K POSITIVE EDGE-TRIGGERED FLIP FLOP WITH SET AND RESET

# RECOMMENDED OPERATING CONDITIONS ( $T_a = -20 - +75 \, ^{\circ}\!\! \text{C}$ , unless otherwise noted )

| Symbol |                           |                        |      | Limits |             |      |  |

|--------|---------------------------|------------------------|------|--------|-------------|------|--|

|        | Parameter                 |                        |      | Тур    | Max         | Unit |  |

| Vçc    | Supply voltage            |                        | 4.75 | 5      | 5.25        | V    |  |

| Lon    | High-level output current | V <sub>OH</sub> ≥ 2.7V | 0    |        | <b>-400</b> | μΔ   |  |

|        | Low-level output current  | V <sub>OL</sub> ≤0.4∨  | 0    |        | 4           | mA   |  |

| LOF    | V <sub>OL</sub> ≤0.5V     |                        | 0    |        | 8           | mA   |  |

#### ELECTRICAL CHARACTERISTICS (Ta = - 20~ + 75°C, unless otherwise noted)

| Symbol          | Parameter                        |                                                    | Test conditions                                                  |                        | Limits |       |         |      |

|-----------------|----------------------------------|----------------------------------------------------|------------------------------------------------------------------|------------------------|--------|-------|---------|------|

|                 |                                  |                                                    | rest condi                                                       | lest conditions        |        | Тур ∗ | Max     | Unit |

| ViH             | High-level input voltage         |                                                    |                                                                  |                        |        |       |         | V    |

| VIL             | Low-level input voltage          |                                                    |                                                                  |                        |        |       | 0.8     | V    |

| VIC             | Input clamp voltage              | out clamp voltage $V_{CC} = 4.75V, I_{IC} = -18mA$ |                                                                  |                        |        | - 1.5 | V       |      |

| V <sub>OH</sub> | High-level output voltage        |                                                    | $V_{CC}=4.75V$ , $V_{I}=0.8V$<br>$V_{I}=2V$ , $I_{OH}=-400\mu A$ |                        | 2.7    | 3.4   |         | ٧    |

| 14.             | Low-level output voltage         |                                                    | V <sub>CC</sub> =4.75V                                           | I <sub>OL</sub> = 4 mA |        | 0.25  | 0.4     | V    |

| VOL             | )L Cow-level output vortage      |                                                    | $V_1 = 0.8 V, V_1 = 2 V$                                         | I <sub>OL</sub> 8 mA   |        | 0.35  | 0.5     | V    |

|                 | J, <b>K</b> , ⊤                  |                                                    | Voc = 5.25V. VI = 2.7V                                           |                        |        | 20    |         |      |

|                 | High-level input current         | S <sub>D.</sub> R <sub>D</sub>                     | S <sub>D.</sub> R <sub>D</sub>                                   |                        |        | 40    | $\mu A$ |      |

| Чн              | J, K, T                          | $V_{\rm CC} = 5.25 V$ , $V_{\rm I} = 10 V$         |                                                                  |                        | 0.1    | 0.1   |         |      |

|                 | SD, RD                           |                                                    |                                                                  |                        |        | 0.2   | mΑ      |      |

|                 |                                  | J, Ř, T                                            |                                                                  |                        |        |       | -0.4    |      |

| I <sub>IL</sub> | Low-level input current          | Sp. Rp                                             | $V_{CC} = 5.25V, V_1 = 0.4V$                                     |                        |        |       | -0.8    | mΑ   |

| los             | Short-circuit output current (No | te 2)                                              | V <sub>CC</sub> = 5.25V, V <sub>O</sub> = 0 V                    |                        | -20    |       | - 100   | mΑ   |

| Tec             | Supply current                   |                                                    | V <sub>CC</sub> = 5.25V, (Note 3)                                |                        |        | 4     | 8       | mΑ   |

$<sup>\</sup>bigstar$  : All typical values are at  $V_{CC} = 5 \ V_{\odot} \ Ta = 25 \ \! ^{\circ}\! C$

#

| Combat           | Parameter                                               | Test conditions                |     | Unit |     |      |

|------------------|---------------------------------------------------------|--------------------------------|-----|------|-----|------|

| Symbol           | rarameter                                               | rest conditions                | Min | Тур  | Max | Unit |

| fmax             | Maximum clock frequency                                 |                                | 25  | 45   |     | MHz  |

| t PLH            | Low-to-high-level, high-to-low-level output propagation | C <sub>L</sub> = 15pF (Note 4) |     | 10   | 25  | ns   |

| t PHL            | time, from T to Q, Q                                    |                                |     | 12   | 40  | ns   |

| t <sub>PLH</sub> | Low-to-high-level, high-to-low-level output propagation |                                |     | 11   | 25  | ns   |

| t PHL            | time, from S <sub>D</sub> , R <sub>D</sub> to Q, Q      |                                |     | 10   | 40  | ns   |

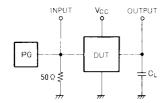

Note 3: Measurement circuit

(1) The pulse generator (PG) has the following characteristics: PRR = 1MHz,  $t_r$  = 6ns,  $t_f$  = 6ns,  $t_w$  = 500ns,  $V_P$  = 3 $V_{P,P}$ ,  $Z_O$  = 50 $\Omega$ .

(2) C<sub>L</sub> includes probe and jig capacitance.

Note 2: All measurements should be done quickly and not more than one output should be shorted at a time.

Note 3: The supply current should be measured with Q and  $\overline{Q}$  alternately set high and with T set low during actual measurement.

# DUAL J-K POSITIVE EDGE-TRIGGERED FLIP FLOP WITH SET AND RESET

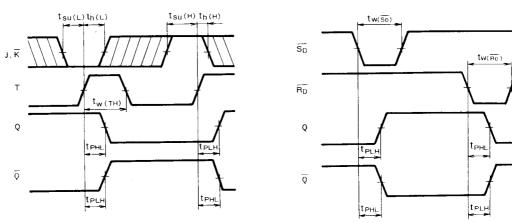

# TIMING REQUIREMENTS ( $V_{CC} = 5 \text{ V}$ , $T_a = 25 \, ^{\circ}\!\! \text{C}$ , unless otherwise noted)

| Symbol             | Parameter                      | Test conditions | Limits |     |     | Unit  |

|--------------------|--------------------------------|-----------------|--------|-----|-----|-------|

|                    |                                |                 | Min    | Тур | Max | Oliit |

| tw(TH)             | Clock input T high pulse width |                 | 25     | 11  |     | ns    |

| tw(sp.Rb)          | Direct set, reset pulse width  |                 | 25     | 4   |     | ns    |

| t <sub>su(H)</sub> | Setup time high to T           |                 | 20     | 19  |     | ns    |

| t <sub>su(L)</sub> | Setup time low to T            |                 | 20     | 7   |     | ns    |

| th(H)              | Hold time high to T            |                 | 5      | - 2 |     | ns    |

| th(L)              | Hold time low to T             |                 | 5      | -16 |     | ns    |

# TIMING DIAGRAM (Reference level = 1.3V)

Note 4: The shaded areas indicate when the input is permitted to change for predictable output performance.

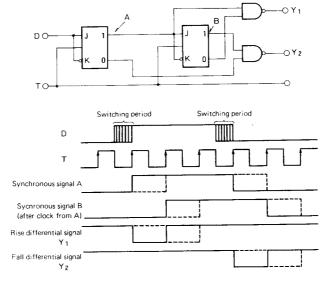

# APPLICATION EXAMPLE

# Typical circuit for converting asynchronous signal into synchronous signal and rise/fall differential circuit

Note 5: The waveforms indicated by the dotted lines apply when reading with the next clock without observing the set-up time to T.

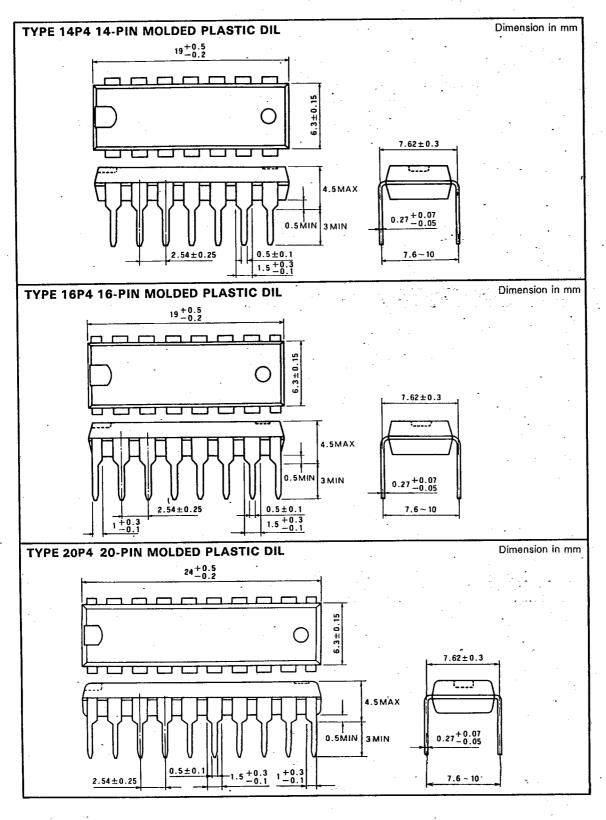

# MITSUBISHI LSTTLs **PACKAGE OUTLINES**

MITSUBISHI {DGTL LOGIC} D7E D 6249827 0013561 3