## LM3940 1A Low Dropout Regulator for 5V to 3.3V Conversion

## **General Description**

N**ational** Semiconductor

The LM3940 is a 1A low dropout regulator designed to provide 3.3V from a 5V supply.

The LM3940 is ideally suited for systems which contain both 5V and 3.3V logic, with prime power provided from a 5V bus.

Because the LM3940 is a true low dropout regulator, it can hold its 3.3V output in regulation with input voltages as low as 4.5V.

The T0-220 package of the LM3940 means that in most applications the full 1A of load current can be delivered without using an additional heatsink.

The surface mount TO-263 package uses minimum board space, and gives excellent power dissipation capability when soldered to a copper plane on the PC board.

### Features

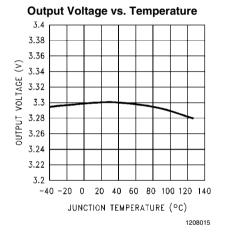

- Output voltage specified over temperature

- Excellent load regulation

- Guaranteed 1A output current

- Requires only one external component

- Built-in protection against excess temperature

- Short circuit protected

## Applications

- Laptop/Desktop Computers

- Logic Systems

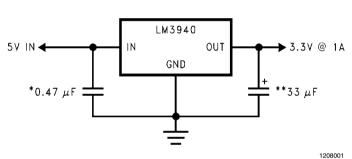

## **Typical Application**

\*Required if regulator is located more than 1 from the power supply filter capacitor or if battery power is used. \*\*See Application Hints.

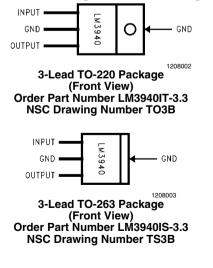

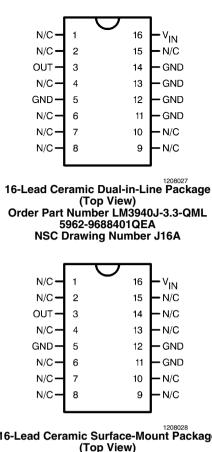

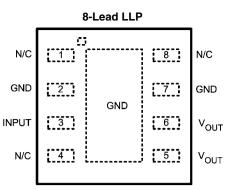

## **Connection Diagram/Ordering Information**

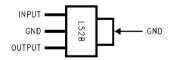

3-Lead SOT-223 (Front View) Order Part Number LM3940IMP-3.3 Package Marked L52B NSC Drawing Number MP04A

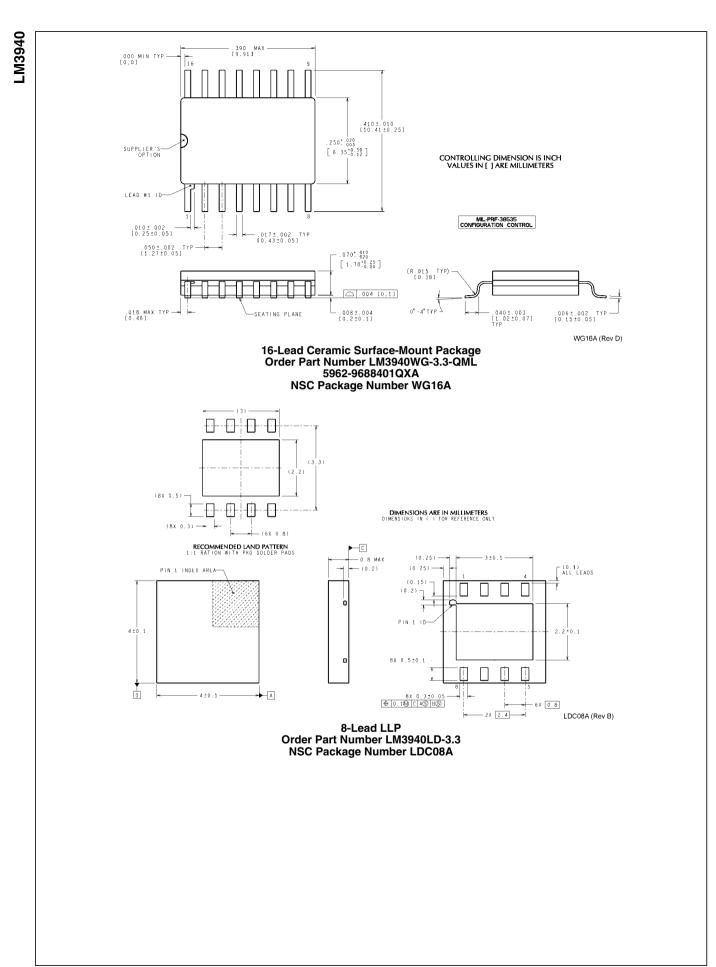

16-Lead Ceramic Surface-Mount Package (Top View) Order Part Number LM3940WG-3.3-QML 5962-9688401QXA NSC Drawing Number WG16A

1208030

Pin 2 and pin 7 are fused to center DAP Pin 5 and 6 need to be tied together on PCB board

(Top View) Order Part Number LM3940LD-3.3 NSC Drawing Number LDC08A

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Storage Temperature Range-65°C to +150°CLead Temperature (Soldering, 5 seconds)260°CPower Dissipation (Note 2)Internally Limited

Input Supply Voltage ESD Rating (Note 3)

7.5V

2 kV

### Operating Ratings (Note 1)

| Junction Temperature Range, $T_J$          | –40°C to +125°C  |

|--------------------------------------------|------------------|

| Input Supply Voltage, V <sub>IN(MIN)</sub> | $V_{O} + V_{DO}$ |

### **Electrical Characteristics**

| Limits in standard typeface are for $T_J = 25^{\circ}C$ , and limits in <b>boldface type</b> | apply over the full operating temperature range. Unless |

|----------------------------------------------------------------------------------------------|---------------------------------------------------------|

| otherwise specified: $V_{IN} = 5V$ , $I_{L} = 1A$ , $C_{OUT} = 33 \ \mu\text{F}$ .           |                                                         |

| Symbol                          | Parameter                   | Conditions                                                                      | Typical | LM3940 (Note 4) |                     | Units   |

|---------------------------------|-----------------------------|---------------------------------------------------------------------------------|---------|-----------------|---------------------|---------|

|                                 |                             |                                                                                 |         | min             | max                 |         |

| Vo                              | Output Voltage              | $5 \text{ mA} \leq \text{I}_{\text{L}} \leq 1 \text{A}$                         | 3.3     | 3.20<br>3.13    | 3.40<br><b>3.47</b> | V       |

| $\frac{\Delta V_O}{\Delta V_I}$ | Line Regulation             | $I_L = 5 \text{ mA}$<br>4.5V $\leq V_{IN} \leq 5.5V$                            | 20      |                 | 40                  | mV      |

| ΔV <sub>O</sub><br>IL           | Load Regulation             | $50 \text{ mA} \leq \text{I}_{\text{L}} \leq 1\text{A}$                         | 35      |                 | 50<br><b>80</b>     |         |

| Z <sub>O</sub>                  | Output Impedance            | I <sub>L</sub> (DC) = 100 mA<br>I <sub>L</sub> (AC) = 20 mA (rms)<br>f = 120 Hz | 35      |                 |                     | mΩ      |

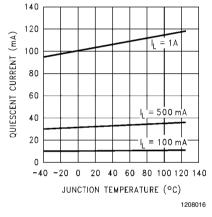

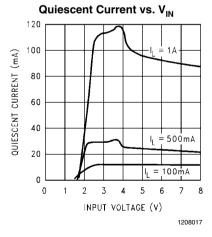

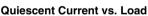

| ۱ <sub>Q</sub>                  | Quiescent Current           | $4.5V \le V_{IN} \le 5.5V$<br>$I_L = 5 \text{ mA}$                              | 10      |                 | 15<br><b>20</b>     | mA      |

|                                 | Quiescent Current           | $V_{IN} = 5V$<br>$I_L = 1A$                                                     | 110     |                 | 200<br><b>250</b>   |         |

| e <sub>n</sub>                  | Output Noise Voltage        | BW = 10 Hz–100 kHz<br>I <sub>L</sub> = 5 mA                                     | 150     |                 |                     | μV (rms |

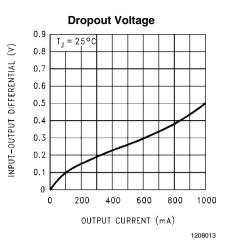

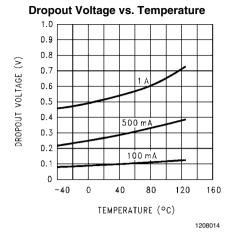

| V <sub>DO</sub>                 | Dropout Voltage<br>(Note 5) | I <sub>L</sub> = 1A                                                             | 0.5     |                 | 0.8<br><b>1.0</b>   | V       |

|                                 |                             | l <sub>L</sub> = 100 mA                                                         | 110     |                 | 150<br><b>200</b>   | mV      |

| I <sub>L</sub> (SC)             | Short Circuit Current       | $R_{L} = 0$                                                                     | 1.7     | 1.2             |                     | А       |

## **Thermal Performance**

| Thermal Resistance<br>Junction-to-Case, θ <sub>JC</sub> | 3-Lead TO-220       | 4  | °C/W |

|---------------------------------------------------------|---------------------|----|------|

|                                                         | 3-Lead TO-263       | 4  | °C/W |

|                                                         | 8-Lead LLP          | 6  | °C/W |

| Thermal Resistance Junction-to-Ambient, $\theta_{JA}$   | 3-Lead TO-220       | 60 | °C/W |

|                                                         | 3-Lead TO-263       | 80 | °C/W |

|                                                         | 8-Lead LLP (Note 2) | 35 | °C/W |

Note 1: Absolute maximum ratings indicate limits beyond which damage to the component may occur. Electrical specifications do not apply when operating the device outside of its rated operating conditions.

**Note 2:** The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_J$ , the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. The value of  $\theta_{JA}$  (for devices in still air with no heatsink) is 60°C/W for the TO-220 package, 80°C/W for the TO-263 package, and 174°C/W for the SOT-223 package. The effective value of  $\theta_{JA}$  can be reduced by using a heatsink (see Application Hints for specific information on heatsinking). The value of  $\theta_{JA}$  for the LLP package is specifically dependant on PCB trace area, trace material, and the number of layers and thermal vias. For improved thermal resistance and power dissipation for the LLP package, refer to Application Note AN-1187. The  $\theta_{JA}$  rating for the LLP is with a JESD51-7 test board having 6 thermal vias under the exposed pad.

Note 3: ESD rating is based on the human body model: 100 pF discharged through 1.5 k $\Omega$ .

Note 4: All limits guaranteed for T<sub>J</sub> = 25°C are 100% tested and are used to calculate Outgoing Quality Levels. All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC) methods.

Note 5: Dropout voltage is defined as the input-output differential voltage where the regulator output drops to a value that is 100 mV below the value that is measured at V<sub>IN</sub> = 5V.

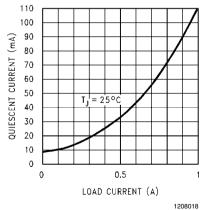

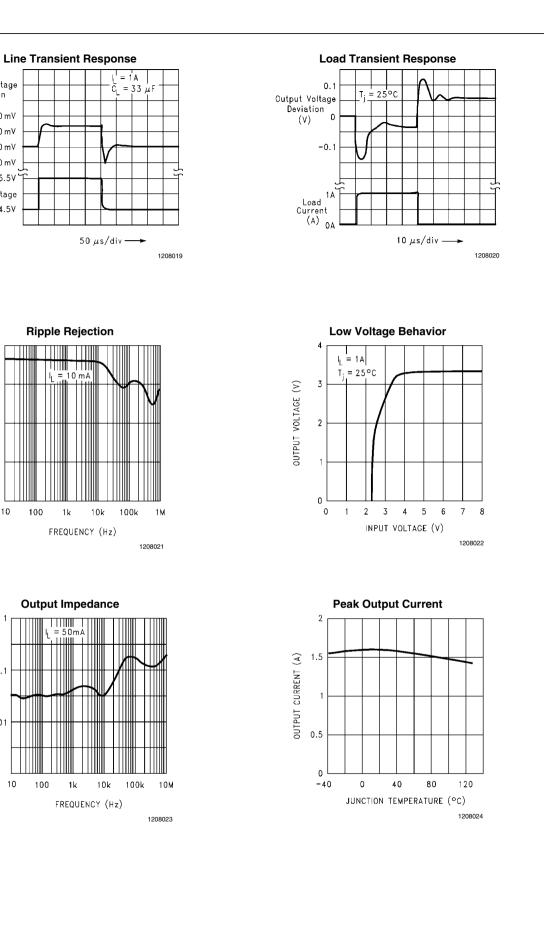

## **Typical Performance Characteristics**

**Quiescent Current vs. Temperature**

www.national.com

Output Voltage Deviation

20 mV 10 mV 0 mV

-10 mV 5.50

Input Voltage (V) 4.5V

40

30

毁 20

10

0

10

1

0.1

0.01

10

OUTPUT IMPEDANCE (D)

LM3940

## **Application Hints**

#### **EXTERNAL CAPACITORS**

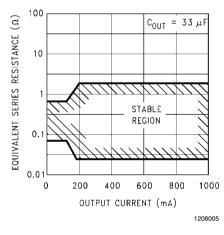

The output capacitor is critical to maintaining regulator stability, and must meet the required conditions for both ESR (Equivalent Series Resistance) and minimum amount of capacitance.

#### MINIMUM CAPACITANCE:

The minimum output capacitance required to maintain stability is 33  $\mu$ F (this value may be increased without limit). Larger values of output capacitance will give improved transient response.

#### ESR LIMITS:

The ESR of the output capacitor will cause loop instability if it is too high or too low. The acceptable range of ESR plotted versus load current is shown in the graph below. It is essential that the output capacitor meet these requirements, or oscillations can result.

**FIGURE 1. ESR Limits**

It is important to note that for most capacitors, ESR is specified only at room temperature. However, the designer must ensure that the ESR will stay inside the limits shown over the entire operating temperature range for the design.

For aluminum electrolytic capacitors, ESR will increase by about 30X as the temperature is reduced from  $25^{\circ}$ C to  $-40^{\circ}$ C. This type of capacitor is not well-suited for low temperature operation.

Solid tantalum capacitors have a more stable ESR over temperature, but are more expensive than aluminum electrolytics. A cost-effective approach sometimes used is to parallel an aluminum electrolytic with a solid Tantalum, with the total capacitance split about 75/25% with the Aluminum being the larger value.

If two capacitors are paralleled, the effective ESR is the parallel of the two individual values. The "flatter" ESR of the Tantalum will keep the effective ESR from rising as quickly at low temperatures.

#### HEATSINKING

A heatsink may be required depending on the maximum power dissipation and maximum ambient temperature of the application. Under all possible operating conditions, the junction temperature must be within the range specified under Absolute Maximum Ratings.

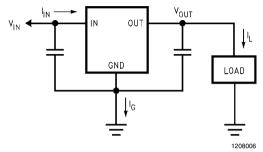

To determine if a heatsink is required, the power dissipated by the regulator,  $P_D$ , must be calculated.

The figure below shows the voltages and currents which are present in the circuit, as well as the formula for calculating the power dissipated in the regulator:

#### FIGURE 2. Power Dissipation Diagram

The next parameter which must be calculated is the maximum allowable temperature rise,  $T_R$  (max). This is calculated by using the formula:

- $T_R (max) = T_J (max) T_A (max)$

- Where: T<sub>J</sub> (max) is the maximum allowable junction temperature, which is 125°C for commercial grade parts.

- T<sub>A</sub> (max) is the maximum ambient temperature which will be encountered in the application.

Using the calculated values for  $T^{}_{R}(max)$  and  $P^{}_{D}$ , the maximum allowable value for the junction-to-ambient thermal resistance,  $\theta^{}_{(JA)}$ , can now be found:

### $\theta_{(JA)} = T_R (max)/P_D$

**IMPORTANT:** If the maximum allowable value for  $\theta_{(JA)}$  is found to be  $\geq 60^{\circ}$ C/W for the TO-220 package,  $\geq 80^{\circ}$ C/W for the TO-263 package, or  $\geq 174^{\circ}$ C/W for the SOT-223 package, no heatsink is needed since the package alone will dissipate enough heat to satisfy these requirements.

If the calculated value for  $\theta_{(JA)} \text{falls}$  below these limits, a heatsink is required.

#### HEATSINKING TO-220 PACKAGE PARTS

The TO-220 can be attached to a typical heatsink, or secured to a copper plane on a PC board. If a copper plane is to be used, the values of  $\theta_{(JA)}$  will be the same as shown in the next section for the TO-263.

If a manufactured heatsink is to be selected, the value of heatsink-to-ambient thermal resistance,  $\theta_{(H-A)},$  must first be calculated:

$\theta_{(H-A)} = \theta_{(JA)} - \theta_{(C-H)} - \theta_{(J-C)}$

- Where:  $\theta_{(J-C)}$  is defined as the thermal resistance from the junction to the surface of the case. A value of 4°C/W can be assumed for  $\theta_{(J-C)}$  for this calculation.

- $\begin{array}{l} \pmb{\theta_{(C-H)}} & \text{is defined as the thermal resistance between} \\ \text{the case and the surface of the heatsink. The} \\ \text{value of } \theta_{(C-H)} \text{ will vary from about } 1.5^{\circ}\text{C/W} \text{ to} \\ \text{about } 2.5^{\circ}\text{C/W} \text{ (depending on method of attachment, insulator, etc.). If the exact value is} \\ \text{unknown, } 2^{\circ}\text{C/W} \text{ should be assumed for } \theta_{(C} \\ \text{-H)^{\circ}} \end{array}$

When a value for  $\theta_{(H-A)}$  is found using the equation shown, *a* heatsink must be selected that has a value that is less than or equal to this number.

$\theta_{(H-A)}$  is specified numerically by the heatsink manufacturer in the catalog, or shown in a curve that plots temperature rise vs. power dissipation for the heatsink.

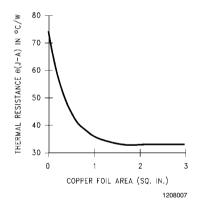

#### HEATSINKING TO-263 AND SOT-223 PACKAGE PARTS

Both the TO-263 ("S") and SOT-223 ("MP") packages use a copper plane on the PCB and the PCB itself as a heatsink. To optimize the heat sinking ability of the plane and PCB, solder the tab of the package to the plane.

Figure 3 shows for the TO-263 the measured values of  $\theta_{(JA)}$  for different copper area sizes using a typical PCB with 1 ounce copper and no solder mask over the copper area used for heatsinking.

#### FIGURE 3. $\theta_{(JA)}$ vs. Copper (1 ounce) Area for the TO-263 Package

As shown in the figure, increasing the copper area beyond 1 square inch produces very little improvement. It should also be observed that the minimum value of  $\theta_{(JA)}$  for the TO-263 package mounted to a PCB is 32°C/W.

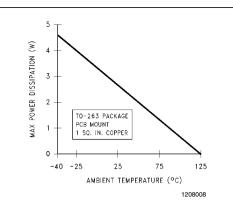

As a design aid, *Figure 4* shows the maximum allowable power dissipation compared to ambient temperature for the TO-263 device (assuming  $\theta_{(JA)}$  is 35°C/W and the maximum junction temperature is 125°C).

## FIGURE 4. Maximum Power Dissipation vs. T<sub>AMB</sub> for the TO-263 Package

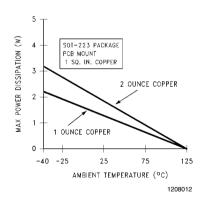

*Figure 5* and *Figure 6* show the information for the SOT-223 package. *Figure 6* assumes a  $\theta_{(JA)}$  of 74°C/W for 1 ounce copper and 51°C/W for 2 ounce copper and a maximum junction temperature of 125°C.

## FIGURE 5. $\theta_{(JA)}$ vs. Copper (2 ounce) Area for the SOT-223 Package

## FIGURE 6. Maximum Power Dissipation vs. T<sub>AMB</sub> for the SOT-223 Package

Please see AN1028 for power enhancement techniques to be used with the SOT-223 package.

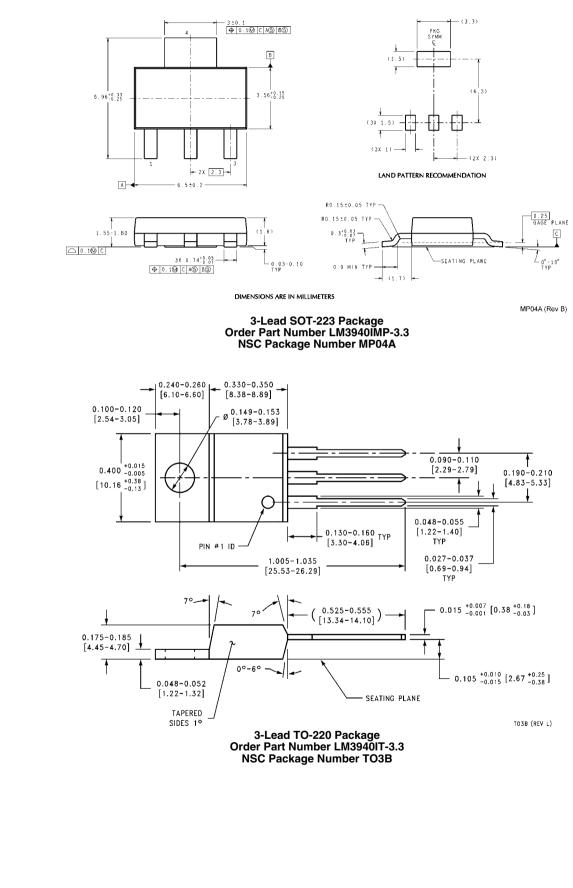

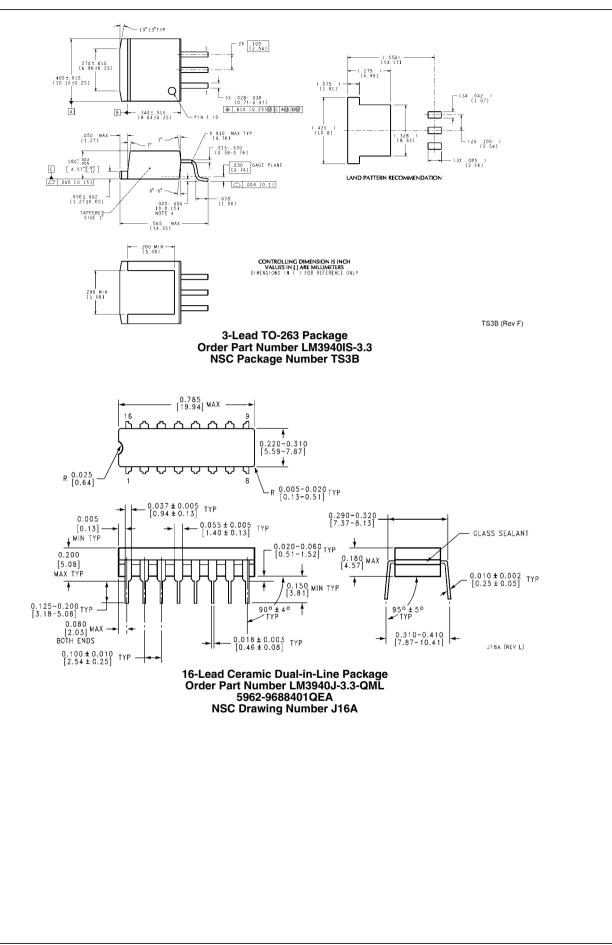

## Physical Dimensions inches (millimeters) unless otherwise noted

LM3940

LM3940

# Notes

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530-85-86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560