# **SIEMENS**

## **Quad Driver Incl. Short-Circuit Signaling**

**FZL 4145 D**

#### **Bipolar IC**

#### **Features**

- Short-circuit shutdown with clock generator

- Four driver circuits for controlling power transistors

- Overload and short-circuit signaling

| Туре       | Ordering Code | Package    |  |  |

|------------|---------------|------------|--|--|

| FZL 4145 D | Q67000-H8437  | P-DIP-18-1 |  |  |

#### **General Description**

The IC comprises four driver circuits capable of driving power transistors for high output currents. The output transistors are protected against short-circuit to ground and supply voltage. The input threshold can be adjusted between 1.5 V and 7 V. Overload or short-circuit failure at an output will be indicated at pin SQ (signaling output).

## **Functional Description**

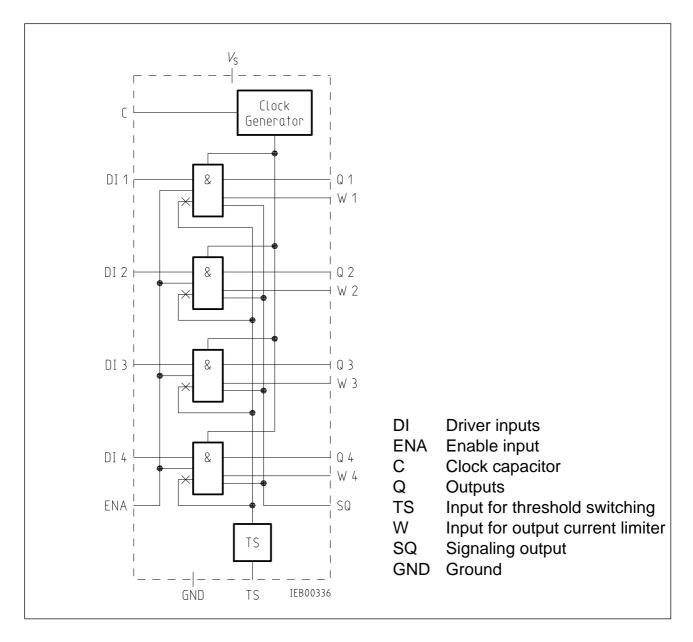

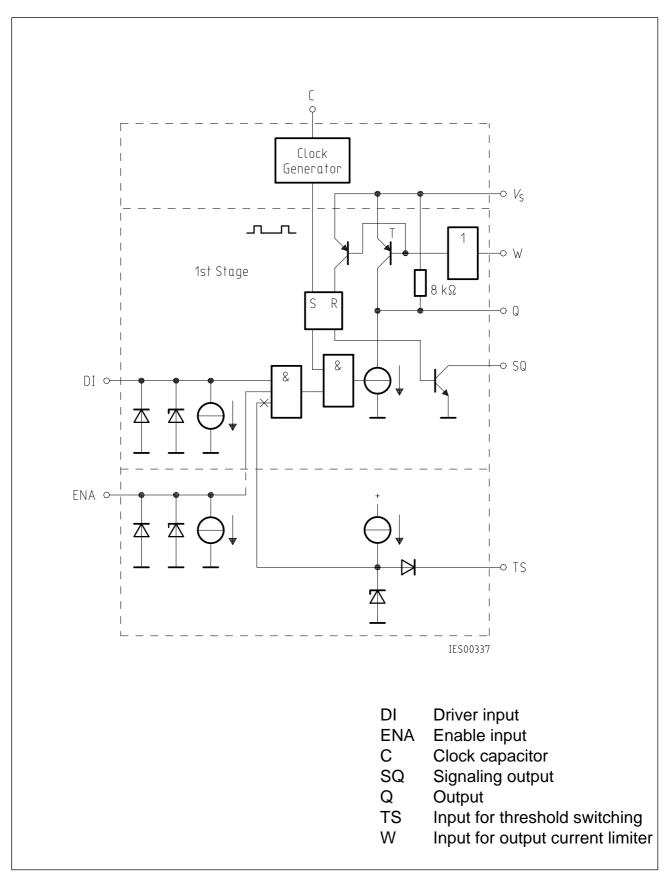

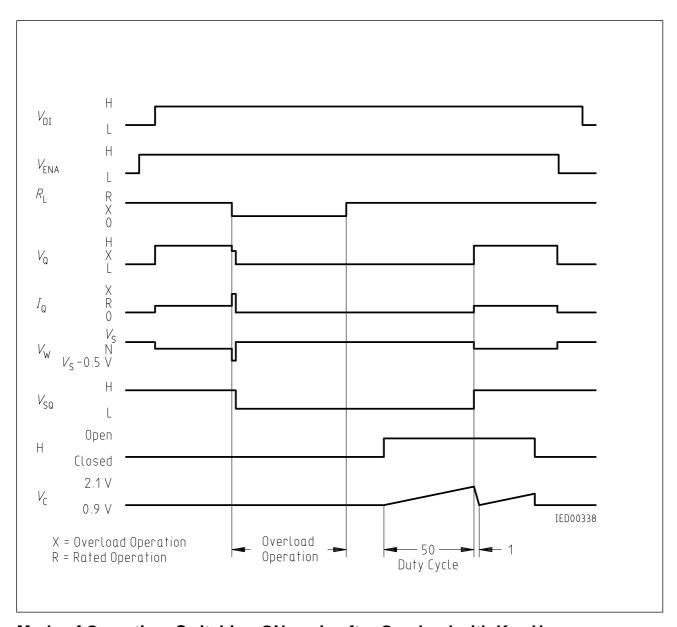

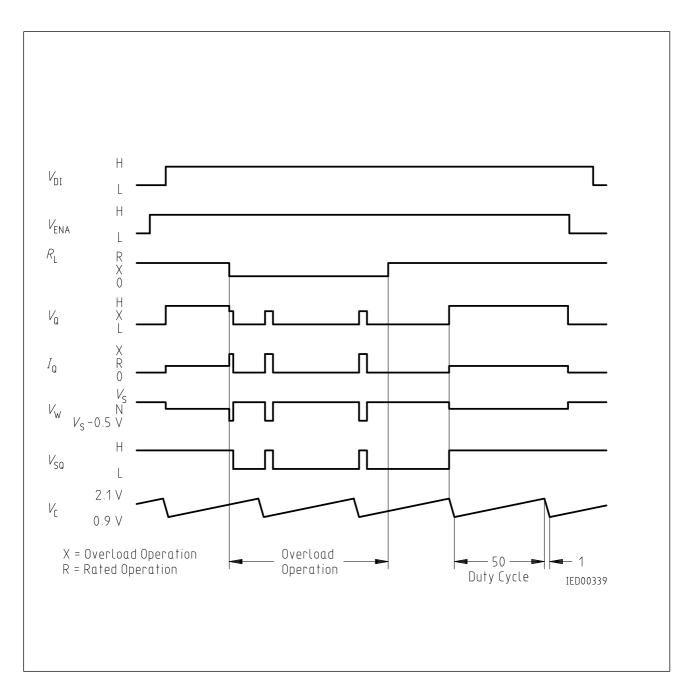

Each driver circuit has one active high driver input DI and a common enable input (ENA) (active high) is provided for all stages. The (Q) outputs are designed to drive the output transistors. The load current is sampled via pin W. If the load current exceeds the preset value, the output stage switches off. Switching-on again is provided by the built-in clock generator. Its operation requires an external capacitor  $C_T$  at pin C. If  $C_T$  is bridged by a break-key, switching on can only be carried out by operating a key. The duty cycle of the clock generator is 1:50 (e.g. 40  $\mu$ s/2 ms with  $C_T$  = 33 nF).

In case of overcurrent or short-circuit failure at any output stage the signaling output (SQ) will go low. In clock-governed operation (i.e. when there is automatic switching on by the clock and not by a key), SQ goes high and low at the clock rate as long as a short-circuit or overload exists. SQ is an open-collector output.

Unused W pins must be connected to  $V_{\rm s}$ . Open W pins would simulate a short-circuit and activate the signaling output.

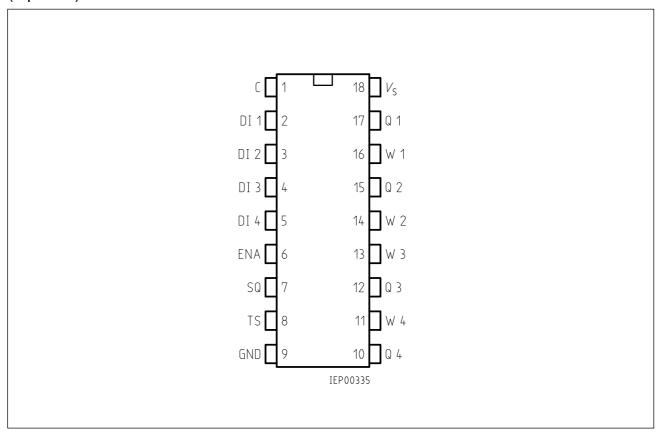

# Pin Configuration (top view)

#### **Block Diagram**

The switching threshold at inputs DI and ENA can be adjusted between 1.5 V and 7 V via connection TS:

$V_{TS} = 0 \text{ V}$ ; input threshold = 1.5 V (for 5 V logic)

$V_{\rm TS}$  = 0 to 5 V; input threshold =  $V_{\rm TS}$  + 1.5 V

$V_{\rm TS}$  =  $V_{\rm S}$ : input threshold = 7 V (for 12/15 V and 24/28 V logic)

If the output is disabled due to the logic states of inputs DI or ENA this disable is effective over the total supply voltage range between  $V_{\rm S}$  = 0 V and  $V_{\rm S}$  = 35 V.

The inputs are protected with clamp diodes.

## **Absolute Maximum Ratings**

| Parameter                               | Symbol                  | Limit Values    |                  | Unit | Remarks                                         |

|-----------------------------------------|-------------------------|-----------------|------------------|------|-------------------------------------------------|

|                                         |                         | min.            | max.             |      |                                                 |

| Supply voltage                          | $V_{S}$                 | - 0.3           | 35               | V    |                                                 |

|                                         | $V_{\mathtt{S}}$        | - 0.3           | 45               | V    | 100 ms duration,<br>1 s interval                |

| Input voltage at DI and ENA             | $V_{\sf DI,\; \sf ENA}$ | - 0.3           | 35               | V    | 1)                                              |

| Voltage at TS and SQ                    | $V_{TS,SQ}$             | - 0.3           | 45               | V    |                                                 |

| Output voltage $V_{Q}$ and voltage at C | $V_{Q},V_{C}$           | - 0.3           | $V_{\mathtt{S}}$ | V    |                                                 |

| Voltage at W                            | $V_{W}$                 | $V_{\rm S}$ – 5 | $V_{	extsf{S}}$  | V    | 3)                                              |

| Input current at DI and ENA             | $I_{\sf DI,\sf ENA}$    | - 3             | 1                | mA   | 2)                                              |

| ·                                       | $I_{DI,ENA}$            | <b>-6</b>       | 2                | mA   | <sup>2)</sup> 100 ms duration,<br>1 s interval  |

|                                         | $I_{\sf DI,\; \sf ENA}$ | <b>-6</b>       | 5                | mA   | <sup>2)</sup> 100 μs duration,<br>1 ms interval |

| Output current at SQ                    | $I_{\sf SQ}$            |                 | 8                | mA   |                                                 |

| Power dissipation of                    |                         |                 |                  |      |                                                 |

| all input diodes                        | $P_{tot}$               |                 | 50               | mW   |                                                 |

| Storage temperature Thermal resistance  | $T_{ m stg}$            | <b>–</b> 65     | 125              | °C   |                                                 |

| system - air                            | $R_{\sf th\;SA}$        |                 | 65               | K/W  |                                                 |

| system - case                           | $R_{th\;SC}$            |                 | 45               | K/W  |                                                 |

## **Operating Range**

| Supply voltage for input threshold | $V_{\mathtt{S}}$                                             | 4.5            | 35       | V      | V 0 V                                                                                                   |

|------------------------------------|--------------------------------------------------------------|----------------|----------|--------|---------------------------------------------------------------------------------------------------------|

| 1.5 V to 6.5 V<br>7 V              | $egin{array}{c} V_{	extsf{S}} \ V_{	extsf{S}} \ \end{array}$ | $V_{TS} + 4.5$ | 35<br>35 | V<br>V | $V_{\text{TS}} = 0 \text{ V}$<br>$V_{\text{TS}} = 0 \text{ V to 5 V}$<br>$V_{\text{TS}} = V_{\text{S}}$ |

| Ambient temperature                | $T_{A}$                                                      | <b>– 25</b>    | 85       | °C     |                                                                                                         |

**Notes:** <sup>1)</sup>  $V_{\rm DI,\;ENA}$  > 35 V requires a protective resistor before DI, ENA. <sup>2)</sup>  $V_{\rm DI,\;ENA}$  may increase to more than 35 V during current nodes. <sup>3)</sup> Unused W connections must be connected to  $V_{\rm S}$ .

## **SIEMENS**

**Characteristics**

Supply voltage 4.5 V  $\leq V_{\rm S} \leq$  30 V

| Parameter                                                                                                            | Symbol                              | Limit Values                 |                              |                   | Unit           | Test                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------|------------------------------|-------------------|----------------|---------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                      |                                     | min.                         | typ.                         | max.              |                | Condition                                                                                                                 |

| Supply current                                                                                                       | $I_{S}$                             |                              | 6                            | 8.5               | mA             | $V_{\rm ENA}$ = 0 V, $V_{\rm W}$ = $V_{\rm S}$                                                                            |

| H-input voltage at DI, ENA<br>H-input voltage at DI, ENA<br>L-input voltage at DI, ENA<br>L-input voltage at DI, ENA | $V_{IH} \ V_{IH} \ V_{IL} \ V_{IL}$ | 2 8                          |                              | 0.7<br>6          | V<br>V<br>V    | $V_{\text{TS}} = 0 \text{ V}$ $V_{\text{TS}} = V_{\text{S}}$ $V_{\text{TS}} = 0 \text{ V}$ $V_{\text{TS}} = V_{\text{S}}$ |

| Input current at DI, ENA                                                                                             | $I_{\sf DI,ENA}$                    | 50                           |                              | 200               | μΑ             | $0.5 \text{ V} \le V_{\text{DI, ENA}}$ $\le 30 \text{ V}$                                                                 |

| L-output voltage at SQ                                                                                               | $V_{\sf SQL}$                       |                              |                              | 0.5               | V              | $I_{\rm SQ}$ = 5 mA                                                                                                       |

| Output current available <sup>1)</sup>                                                                               | $I_{Q}$ $I_{Q}$                     | 1.5<br>1.7                   | 2.5                          |                   | mA<br>mA       | $V_{Q} = V_{S} - 1.5 \text{ V}$<br>$T_{A} = 0 \text{ °C}$<br>$V_{Q} = V_{S} - 1.5 \text{ V}$                              |

| Current from TS                                                                                                      | $-I_{TS}$                           |                              | 2                            | 10                | μΑ             | $V_{\text{TS}} = 0 \text{ V}$                                                                                             |

| Switching threshold at W                                                                                             | $V_{W}$                             | $V_{\rm S}$ – 0.6            | $V_{\rm S}$ – 0.5            | $V_{\rm S}$ – 0.4 | V              |                                                                                                                           |

| Current in W Current from C Current in C                                                                             | $I_{ m W} - I_{ m C}$ $I_{ m C}$    | 12<br>0.6                    | 20<br>1                      | 100<br>34<br>1.7  | μΑ<br>μΑ<br>mA | T <sub>A</sub> = 20 °C<br>T <sub>A</sub> = 20 °C                                                                          |

| Upper switching threshold at C Lower switching                                                                       | $V_{	extsf{CU}}$                    | 1.6                          | 2.1                          | 1.7               | V              | <i>T</i> <sub>A</sub> = 20 °C                                                                                             |

| threshold at C Saturation voltage at T <sup>2)</sup>                                                                 | $V_{	extsf{CL}} \ V_{	extsf{Q R}}$  | 0.6                          | $0.9 \ V_{\rm S}$ – $0.3$    | 1.2               | V<br>V         | $T_{\rm A}$ = 20 °C<br>$V_{\rm W}$ = $V_{\rm S}$ - 2 V,<br>$I_{\rm Q}$ = 0                                                |

| H-output voltage                                                                                                     | $V_{QH}$                            | <i>V</i> <sub>S</sub> – 0.25 | <i>V</i> <sub>S</sub> – 0.02 |                   | V              | $V_{\text{ENA}} = 0 \text{ V}$                                                                                            |

The actual output current is typically 0.5 mA higher, a value which is required as current for the short-circuit protection. However, only the value specified above is available to drive the external output transistors.

<sup>2)</sup> See block diagram

## **Schematic Circuit Diagram of One Stage**

Mode of Operation: Switching-ON again after Overload with Key H

Mode of Operation: Automatic Switching-ON again after Overload

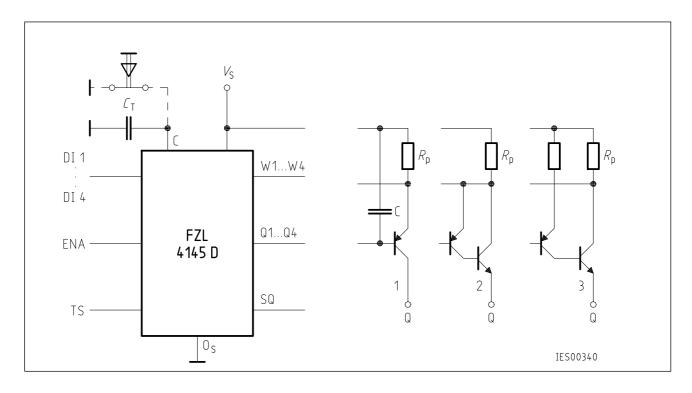

### **Typical Application Circuits**

The load conditions at Q depend on the permissible power dissipation of the used power transistors. The pulsed power dissipation in case of a short circuit must be observed.

In order to suppress oscillations of the power stage in case of a short circuit, a capacitor C at Q1 to Q4 is necessary if e.g. fast switching transistors are used.

Typical value X of C: approx. 20 nF.

The output circuit 1 is suited for currents up to approx.  $I_Q = 100$  mA.

The output circuit 2 and 3 are suited for currents up to approx.  $I_Q = 2$  A. A minimum power dissipation can be achieved with circuit 3.

A break key in parallel to  $C_T$  allows a manual switch-on in case of short-circuit.

$R_{\rm P}$  = Precision resistor (current measurement)

$C_{\rm T} = 0.8 \, {\rm x} \, t_{\rm p} \, ({\rm nF}, \, {\rm \mu s})$

t<sub>p</sub> = Short-circuit current pulse length

**Note:** Circuit 1 does not permit a capacitor between Q1 and Q4 and the collector. Circuit 2 does not permit a capacitor between Q1 and Q4 and base or emitter, respectively.

Otherwise too high current spikes would arise in case of a short circuit.

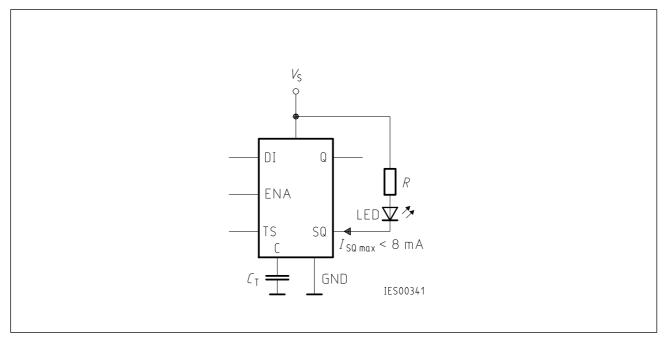

## Typical Application of Short-Circuit Signaling Output SQ

## 1. LED Display

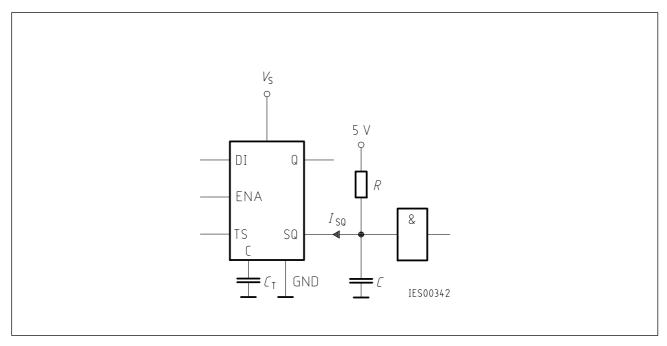

#### 2. TTL/CMOS/LSL Driving

If the pulses appearing at SQ during clocked operation disturb the remainder of the circuit, a lowpass filter will be necessary. For a load current of  $I_{\rm SQ}$  = 1 mA a capacitor C of approx. 10 nF is necessary to limit the output pulses of up to 10  $\mu$ s (depending on  $C_{\rm T}$ ) to 1 V. Signaling occurs after approx. 50  $\mu$ s.