# 200 kHz, 1 A High Voltage Step-Down Switching Regulator

Data Sheet ADP3050

#### **FEATURES**

Wide input voltage range: 3.6 V to 30 V

Adjustable and fixed (3.3 V, 5 V) output options

Integrated 1 A power switch

Uses small surface-mount components

Cycle-by-cycle current limiting

Peak input voltage (100 ms): 60 V

Configurable as a buck, buck-boost, and SEPIC

regulator

Available in 8-lead SOIC package

Supported by ADIsimPower™ design tool

#### **APPLICATIONS**

Industrial power systems

PC peripheral power systems

Preregulator for linear regulators

Distributed power systems

Automotive systems

Battery chargers

# GENERAL DESCRIPTION

The ADP3050 is a current mode monolithic buck (step down) PWM switching regulator that contains a high current 1 A power switch and all control, logic, and protection functions. It uses a unique compensation scheme allowing the use of any type of output capacitor (tantalum, ceramic, electrolytic, OS-CON). Unlike some buck regulators, the design is not restricted to using a specific type of output capacitor or ESR value.

A special boosted drive stage is used to saturate the NPN power switch, providing a system efficiency higher than conventional bipolar buck switchers. Further efficiency improvements are obtained by using the low voltage regulated output to provide the internal operating current of the device. A high switching frequency allows the use of small external surface-mount components. A wide variety of standard off-the-shelf devices can be used, providing a great deal of design flexibility. A complete regulator design requires only a few external components.

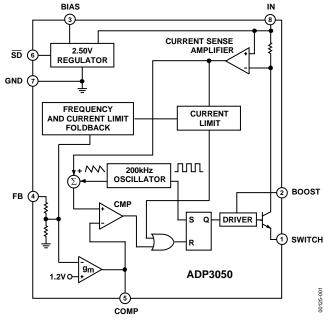

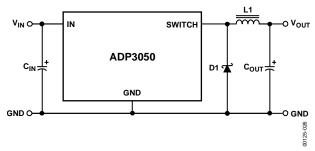

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

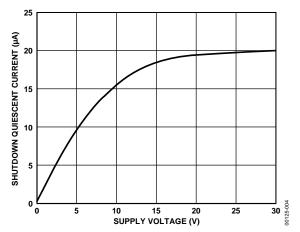

The ADP3050 includes a shutdown input that places the device in a low power mode, reducing the total supply current to under 20  $\mu A.$  Internal protection features include thermal shutdown circuitry and a cycle-by-cycle current limit for the power switch to provide complete device protection under fault conditions.

The ADP3050 provides excellent line and load regulation, maintaining typically less than  $\pm 3\%$  output voltage accuracy over temperature and under all input voltage and output current conditions.

The ADP3050 is specified over the industrial temperature range of -40°C to +85°C and is available in a thermally enhanced 8-lead (not Pb-free only) SOIC package and a standard 8-lead (Pb-free only) RoHS-compliant SOIC package.

# **TABLE OF CONTENTS**

| Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Functional Block Diagram 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Absolute Maximum Ratings 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ESD Caution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Pin Configuration and Function Descriptions5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Typical Performance Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Theory of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Setting the Output Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Applications Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ADIsimPower Design Tool11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Inductor Selection11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Output Capacitor Selection12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| REVISION HISTORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| REVISION HISTORY 6/12—Rev. B to Rev. C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6/12—Rev. B to Rev. C Change to Features Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6/12—Rev. B to Rev. C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6/12—Rev. B to Rev. C Change to Features Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6/12—Rev. B to Rev. C Change to Features Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6/12—Rev. B to Rev. C Change to Features Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6/12—Rev. B to Rev. C Change to Features Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6/12—Rev. B to Rev. C Change to Features Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6/12—Rev. B to Rev. C Change to Features Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6/12—Rev. B to Rev. C         Change to Features Section       1         Added ADIsimPower Design Tool Section       11         Changes to Ordering Guide       20         3/08—Rev. A to Rev. B       Updated Format       Universal         Changes to General Description Section       1         Changes to Figure 3 and Figure 5       6         Changes to Table 2       4         Deleted Table 4       14                                                                                                                                                                  |

| 6/12—Rev. B to Rev. C         Change to Features Section       1         Added ADIsimPower Design Tool Section       11         Changes to Ordering Guide       20         3/08—Rev. A to Rev. B       Universal         Updated Format       Universal         Changes to General Description Section       1         Changes to Figure 3 and Figure 5       6         Changes to Table 2       4         Deleted Table 4       14         Changes to Table 5       15                                                                                                            |

| 6/12—Rev. B to Rev. C         Change to Features Section       1         Added ADIsimPower Design Tool Section       11         Changes to Ordering Guide       20         3/08—Rev. A to Rev. B       Universal         Updated Format       Universal         Changes to General Description Section       1         Changes to Figure 3 and Figure 5       6         Changes to Table 2       4         Deleted Table 4       14         Changes to Table 5       15         Deleted Table 8       15                                                                           |

| 6/12—Rev. B to Rev. C         Change to Features Section       1         Added ADIsimPower Design Tool Section       11         Changes to Ordering Guide       20         3/08—Rev. A to Rev. B       Universal         Updated Format       Universal         Changes to General Description Section       1         Changes to Figure 3 and Figure 5       6         Changes to Table 2       4         Deleted Table 4       14         Changes to Table 5       15         Deleted Table 8       15         Deleted Table 7       16                                          |

| 6/12—Rev. B to Rev. C         Change to Features Section       1         Added ADIsimPower Design Tool Section       11         Changes to Ordering Guide       20         3/08—Rev. A to Rev. B       Universal         Updated Format       Universal         Changes to General Description Section       1         Changes to Figure 3 and Figure 5       6         Changes to Table 2       4         Deleted Table 4       14         Changes to Table 5       15         Deleted Table 8       15         Deleted Table 7       16         Deleted Table 9       16         |

| 6/12—Rev. B to Rev. C         Change to Features Section       1         Added ADIsimPower Design Tool Section       11         Changes to Ordering Guide       20         3/08—Rev. A to Rev. B       Updated Format       Universal         Changes to General Description Section       1         Changes to Figure 3 and Figure 5       6         Changes to Table 2       4         Deleted Table 4       14         Changes to Table 5       15         Deleted Table 8       15         Deleted Table 9       16         Changes to Boosted Drive Stage Section and Thermal |

| 6/12—Rev. B to Rev. C         Change to Features Section       1         Added ADIsimPower Design Tool Section       11         Changes to Ordering Guide       20         3/08—Rev. A to Rev. B       Universal         Updated Format       Universal         Changes to General Description Section       1         Changes to Figure 3 and Figure 5       6         Changes to Table 2       4         Deleted Table 4       14         Changes to Table 5       15         Deleted Table 8       15         Deleted Table 7       16         Deleted Table 9       16         |

| Catch Diode Selection            | 13 |

|----------------------------------|----|

| Input Capacitor Selection        | 14 |

| Discontinous Mode Ringing        | 14 |

| Setting the Output Voltage       | 14 |

| Frequency Compensation           | 14 |

| Current Limit/Frequency Foldback | 15 |

| Bias Pin Connection              | 15 |

| Boosted Drive Stage              | 15 |

| Start-Up/Minimum Input Voltage   | 15 |

| Thermal Considerations           | 10 |

| Board Layout Guidelines          | 17 |

| Typical Applications             | 17 |

| Inverting (Buck Boost) Regulator | 18 |

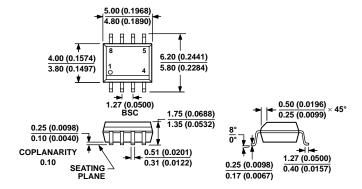

| Outline Dimensions               | 20 |

| Ordering Guide                   | 20 |

# **SPECIFICATIONS**

$V_{\rm IN}$  = 10 V,  $T_{\rm A}$  = -40°C to +85°C, unless otherwise noted.

Table 1.

| Parameter <sup>1</sup>                 | Symbol                | Conditions                                              | Min  | Тур   | Max  | Unit |

|----------------------------------------|-----------------------|---------------------------------------------------------|------|-------|------|------|

| FEEDBACK                               |                       |                                                         |      |       |      |      |

| Feedback Voltage                       | $V_{FB}$              | Over line and temperature                               |      |       |      |      |

| ADP3050                                |                       |                                                         | 1.16 | 1.20  | 1.24 | V    |

| ADP3050-3.3                            |                       |                                                         | 3.20 | 3.30  | 3.40 | V    |

| ADP3050-5                              |                       |                                                         | 4.85 | 5.00  | 5.15 | V    |

| Line Regulation                        |                       | $V_{IN} = 10 \text{ V}$ to 30 V, no load                |      | 0.005 |      | %/V  |

| Load Regulation                        |                       | I <sub>LOAD</sub> = 100 mA to 1 A, ADP3050AR only       | -1.0 | +0.1  | +1.0 | %/A  |

|                                        |                       | ADP3050AR-3.3, ADP3050AR-5                              | -0.5 | +0.1  | +0.5 | %/A  |

| Input Bias Current                     | I <sub>FB</sub>       | ADP3050AR only                                          |      | 0.65  | 2    | μΑ   |

| ERROR AMPLIFIER                        |                       |                                                         |      |       |      |      |

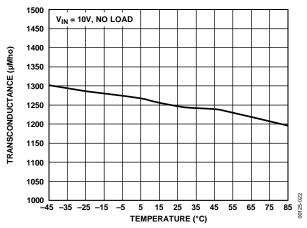

| Transconductance <sup>2</sup>          | g <sub>m</sub>        |                                                         |      | 1250  |      | μMho |

| Voltage Gain <sup>2</sup>              | A <sub>VOL</sub>      |                                                         |      | 300   |      | V/V  |

| Output Current                         |                       |                                                         |      |       |      |      |

| ADP3050                                |                       | COMP = 1.0 V, FB = 1.1 V to 1.3 V                       |      | ±115  |      | μΑ   |

| ADP3050-3.3                            |                       | COMP = 1.0  V, FB = 3.0  V to  3.6  V                   |      | ±120  |      | μΑ   |

| ADP3050-5                              |                       | COMP = 1.0  V, FB = 4.5  V to  5.5  V                   |      | ±135  |      | μΑ   |

| OSCILLATOR                             |                       |                                                         |      |       |      | -    |

| Oscillator Frequency <sup>3</sup>      | fosc                  |                                                         | 170  | 200   | 240  | kHz  |

| Minimum Duty Cycle                     | D <sub>MIN</sub>      |                                                         |      | 10    |      | %    |

| Maximum Duty Cycle                     | D <sub>MAX</sub>      |                                                         |      | 90    |      | %    |

| SWITCH                                 |                       |                                                         |      |       |      |      |

| Average Output Current Limit⁴          | I <sub>CL(AVG)</sub>  |                                                         |      |       |      |      |

| ADP3050                                |                       | BOOST = 15 V, FB = 1.1 V                                | 1.0  | 1.25  | 1.5  | Α    |

| ADP3050-3.3                            |                       | BOOST = 15 V, FB = 3.0 V                                | 1.0  | 1.25  | 1.5  | Α    |

| ADP3050-5                              |                       | BOOST = 15 V, FB = 4.5 V                                | 1.0  | 1.25  | 1.5  | Α    |

| Peak Switch Current Limit <sup>5</sup> | I <sub>CL(PEAK)</sub> |                                                         | 1.5  | 1.7   | 2.1  | Α    |

| Saturation Voltage                     |                       | $BOOST = 15 V$ , $I_{LOAD} = 1 A$                       |      | 0.65  | 0.95 | V    |

| Leakage Current                        |                       |                                                         |      | 50    |      | nA   |

| SHUTDOWN                               |                       |                                                         |      |       |      |      |

| Input Voltage Low                      |                       |                                                         |      |       | 0.4  | V    |

| Input Voltage High                     |                       |                                                         | 2.0  |       |      | V    |

| SUPPLY                                 |                       |                                                         |      |       |      |      |

| Input Voltage Range <sup>6</sup>       | V <sub>IN</sub>       |                                                         | 3.6  |       | 30   | ٧    |

| Minimum BIAS Voltage                   | $V_{BIAS}$            |                                                         |      |       | 3.0  | ٧    |

| Minimum BOOST Voltage                  | $V_{BOOST}$           |                                                         |      |       | 3.0  | ٧    |

| IN Supply Current                      | IQ                    |                                                         |      |       |      |      |

| Normal Mode                            |                       | BIAS = 5.0 V                                            |      | 0.7   | 1.5  | mA   |

| Shutdown Mode                          |                       | $\overline{SD} = 0 \text{ V, V}_{IN} \leq 30 \text{ V}$ |      | 15    | 40   | μΑ   |

| BIAS Supply Current                    | I <sub>BIAS</sub>     | BIAS = 5.0 V                                            |      | 4.0   | 6.0  | mA   |

| BOOST Supply Current                   | I <sub>BOOST</sub>    | BOOST = 15 V, I <sub>SW</sub> = 0.5 A                   |      | 18    |      | mA   |

| ,                                      |                       | BOOST = 15 V, I <sub>SW</sub> = 1.0 A                   |      | 20    | 40   | mA   |

<sup>&</sup>lt;sup>1</sup> All limits at temperature extremes are guaranteed via correlation using standard statistical quality control (SQC).

<sup>&</sup>lt;sup>2</sup> Transconductance and voltage gain measurements refer to the internal amplifier without the voltage divider. To calculate the transconductance and gain of the fixed voltage parts, divide the values shown by FB/1.20.

$<sup>^3</sup>$  The switching frequency is reduced when the feedback pin is lower than  $0.8 \times FB$ .

<sup>&</sup>lt;sup>4</sup> See Figure 24 for typical application circuit.

<sup>&</sup>lt;sup>5</sup> Switch current limit is measured with no diode, no inductor, and no output capacitor.

<sup>&</sup>lt;sup>6</sup> Minimum input voltage is not measured directly, but is guaranteed by other tests. The actual minimum input voltage needed to keep the output in regulation depends on output voltage and load current.

# **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                                | Rating               |

|------------------------------------------|----------------------|

| IN Voltage                               |                      |

| Continuous                               | −0.3 V to +40 V      |

| Peak (<100 ms)                           | −0.3 V to +60 V      |

| BOOST Voltage                            |                      |

| Continuous                               | −0.3 V to +45 V      |

| Peak (<100 ms)                           | −0.3 V to +65 V      |

| SD, BIAS Voltage                         | -0.3 V to IN + 0.3 V |

| FB Voltage                               | −0.3 V to +8 V       |

| COMP Voltage                             | -0.3 V to IN + 0.3 V |

| SWITCH Voltage                           | -0.3 V to IN + 0.3 V |

| Operating Ambient Temperature Range      | −40°C to +85°C       |

| Operating Junction Temperature Range     | −40°C to +125°C      |

| Storage Temperature Range                | −65°C to +150°C      |

| $\theta_{JA}$ (4-Layer PCB) <sup>1</sup> | 60.6°C/W             |

| $\theta_{JA}$ (4-Layer PCB) <sup>2</sup> | 87.5°C/W             |

| Lead Temperature (Soldering, 60 sec)     | 300°C                |

<sup>&</sup>lt;sup>1</sup> Applied to all models that are not Pb-free.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> Applied to all Pb-free models.

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

# **Table 3. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                         |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | SWITCH   | Switch Node. This pin is the emitter of the internal NPN power switch. The voltage at this pin switches between $V_{IN}$ and approximately $-0.5$ V.                                                                                                                                                                                                                |

| 2       | BOOST    | Boost Pin. This pin is used to provide a boosted voltage (higher than $V_{IN}$ ) for the drive stage of the NPN power switch. With the higher drive voltage, the power switch can be saturated, greatly reducing the switch power losses.                                                                                                                           |

| 3       | BIAS     | Bias Input Pin. Connect this pin to the regulated output voltage to maximize system efficiency. When this pin is above 2.7 V, most of the ADP3050 operating current is taken from the output instead of the input supply. Leave unconnected if not used.                                                                                                            |

| 4       | FB       | Feedback Pin. This feedback pin senses the regulated output voltage. Connect this pin directly to the output (fixed output versions).                                                                                                                                                                                                                               |

| 5       | COMP     | Compensation Node. This pin is used to compensate the regulator with an external resistor and capacitor. This pin is also used to override the control loop. However, the voltage on this pin should not exceed 2 V, because the pin is internally clamped to ensure a fast transient response. Use a pull-up resistor if this pin is to be pulled higher than 2 V. |

| 6       | SD       | Shutdown Pin. Use this pin to turn the device on and off. If this feature is not needed, tie this pin directly to IN.                                                                                                                                                                                                                                               |

| 7       | GND      | Ground Pin. Connect this pin to local ground plane.                                                                                                                                                                                                                                                                                                                 |

| 8       | IN       | Power Input. Connect this pin to the input supply voltage. An input bypass capacitor must be placed close to this pin to ensure proper regulator operation.                                                                                                                                                                                                         |

# TYPICAL PERFORMANCE CHARACTERISTICS

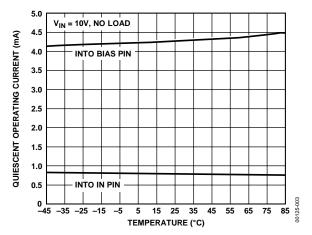

Figure 3. Quiescent Operating Current vs. Temperature

Figure 4. Shutdown Quiescent Current vs. Supply Voltage

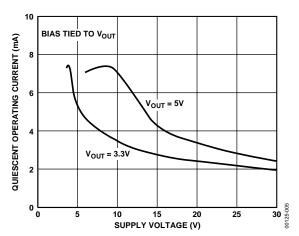

Figure 5. Quiescent Operating Current vs. Supply Voltage

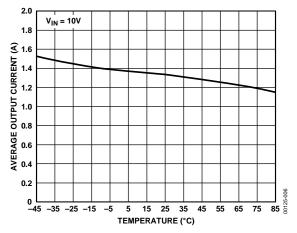

Figure 6. Average Output Current Limit vs. Temperature

Figure 7. Boost Current vs. Load Current

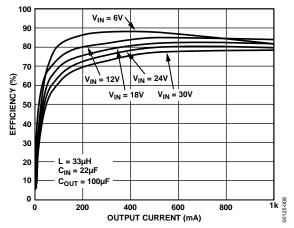

Figure 8. 5 V Output Efficiency

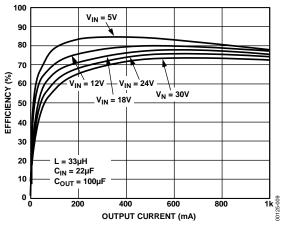

Figure 9. 3.3 V Output Efficiency

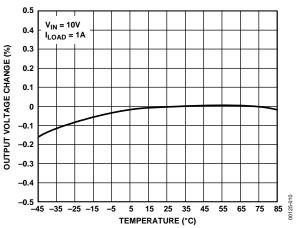

Figure 10. Output Voltage Change vs. Temperature

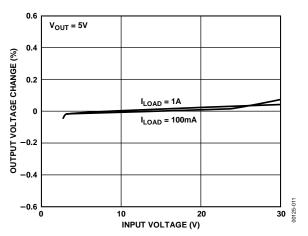

Figure 11.5 V Output Voltage Change vs. Input Voltage

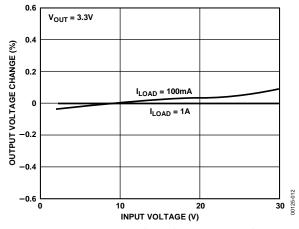

Figure 12. 3.3 V Output Voltage Change vs. Input Voltage

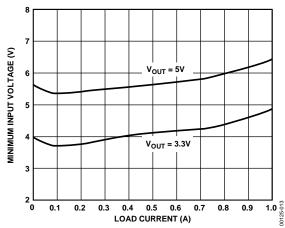

Figure 13. Minimum Input Voltage vs. Load Current

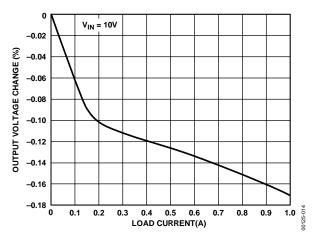

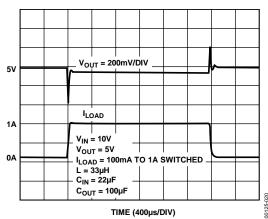

Figure 14. Load Regulation

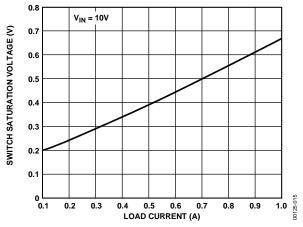

Figure 15. Switch Saturation Voltage vs. Load Current

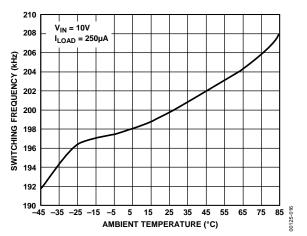

Figure 16. Switching Frequency vs. Temperature

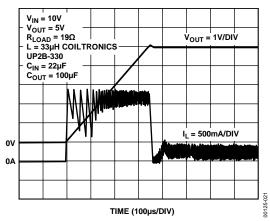

0V

I<sub>L</sub> = 500mA/DIV

V<sub>IN</sub> = 10V

V<sub>OUT</sub> = 5V

I<sub>LOAD</sub> = 800mA

L = 33μH

C<sub>IN</sub> = 22μF

C<sub>OUT</sub> = 100μF

TIME (1μs/DIV)

Figure 18. Continuous Conduction Mode Waveforms

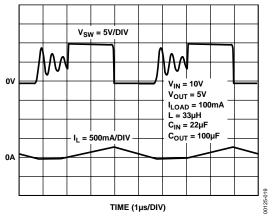

Figure 19. Discontinuous Conduction Mode Waveforms

Figure 20. Transient Response

Figure 21. Start-Up from Shutdown

Figure 22. Error Amplifier Transconductance vs. Temperature

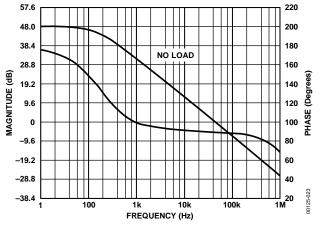

Figure 23. Error Amplifier Gain

# THEORY OF OPERATION

The ADP3050 is a fixed frequency, current mode buck regulator. Current mode systems provide excellent transient response, and are much easier to compensate than voltage mode systems (refer to Figure 1). At the beginning of each clock cycle, the oscillator sets the latch, turning on the power switch. The signal at the noninverting input of the comparator is a replica of the switch current (summed with the oscillator ramp). When this signal reaches the appropriate level set by the output of the error amplifier, the comparator resets the latch and turns off the power switch. In this manner, the error amplifier sets the correct current trip level to keep the output in regulation. If the error amplifier output increases, more current is delivered to the output; if it decreases, less current is delivered to the output.

The current sense amplifier provides a signal proportional to switch current to both the comparator and to a cycle-by-cycle current limit. If the current limit is exceeded, the latch is reset, turning the switch off until the beginning of the next clock cycle. The ADP3050 has a foldback current limit that reduces the switching frequency under fault conditions to reduce stress to the IC and to the external components.

Most of the control circuitry is biased from the 2.5 V internal regulator. When the BIAS pin is left open, or when the voltage at this pin is less than 2.7 V, all of the operating current for the ADP3050 is drawn from the input supply. When the BIAS pin is above 2.7 V, the majority of the operating current is drawn from this pin (usually tied to the low voltage output of the regulator) instead of from the higher voltage input supply. This can provide substantial efficiency improvements at light load conditions, especially for systems where the input voltage is much higher than the output voltage.

The ADP3050 uses a special drive stage allowing the power switch to saturate. An external diode and capacitor provide a boosted voltage to the drive stage that is higher than the input supply voltage. Overall efficiency is dramatically improved by using this type of saturating drive stage.

Pulling the  $\overline{SD}$  pin below 0.4 V puts the device in a low power mode, shutting off all internal circuitry and reducing the supply current to under 20  $\mu$ A.

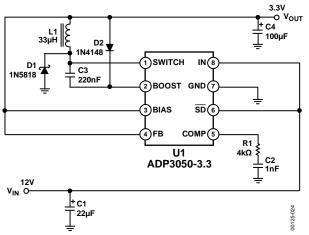

Figure 24. Typical Application Circuit

# **SETTING THE OUTPUT VOLTAGE**

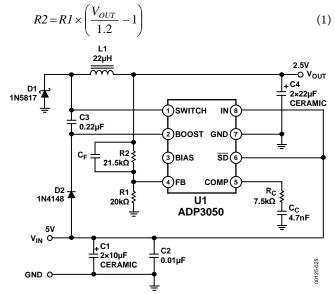

The output of the adjustable version (ADP3050AR and ADP3050ARZ) can be set to any voltage between 1.25 V and 12 V by connecting a resistor divider to the FB pin as shown in Figure 25.

Figure 25. Adjustable Output Application Circuit

# APPLICATIONS INFORMATION

# **ADIsimPower DESIGN TOOL**

The ADP3050 is supported by the ADIsimPower design tool set. ADIsimPower is a collection of tools that produce complete power designs optimized for a specific design goal. The tools enable the user to generate a full schematic, bill of materials, and calculate performance in minutes. ADIsimPower can optimize designs for cost, area, efficiency, and parts count while taking into consideration the operating conditions and limitations of the IC and all real external components. For more information about ADIsimPower design tools, refer to www.analog.com/ADIsimPower. The tool set is available from this website, and users can request an unpopulated board through the tool.

The complete process for designing a step-down switching regulator using the ADP3050 is provided in the following sections. Each section includes a list of recommended devices. These lists do not include every available device or manufacturer. They contain only surface-mount devices. Equivalent throughhole devices can be substituted if needed. In choosing components, keep in mind what is most important to the design, for example, efficiency, cost, and size. These ultimately determine which components are used. It is also important to ensure that the design specifications are clearly defined and reflect the worst-case conditions. Key specifications include the minimum and maximum input voltage, the output voltage and ripple, and the minimum and maximum load current.

# **INDUCTOR SELECTION**

The inductor value determines the mode of operation for the regulator: continuous mode, where the inductor current flows continuously; or discontinuous mode, where the inductor current reduces to zero during every switch cycle. Continuous mode is the best choice for many applications. It provides higher output power, lower peak currents in the switch, inductor, and diode, and a lower inductor ripple current, which means lower output ripple voltage. Discontinuous mode allows the use of smaller magnetics, but at a price: lower available load current and higher peak and ripple currents. Designs with a high input voltage or a low load current often operate in discontinuous mode to minimize inductor value and size. The ADP3050 is designed to work well in both modes of operation.

# **Continuous Mode**

The inductor current in a continuous mode system is a triangular waveform (equal to the ripple current) centered around a dc value (equal to the load current). The amount of ripple current is determined by the inductor value, and is usually between 20% and 40% of the maximum load current. To reduce the inductor size, ripple currents between 40% and 80% are often used in continuous mode designs with a high input voltage or a low output current.

The inductor value is calculated using the following equation:

$$L = \frac{V_{IN(MAX)} - V_{OUT}}{I_{RIPPLE}} \times \frac{1}{f_{SW}} \times \frac{V_{OUT}}{V_{IN(MAX)}}$$

(2)

Where  $V_{IN(MAX)}$  is the maximum input voltage,  $V_{OUT}$  is the regulated output voltage, and  $f_{SW}$  is the switching frequency (200 kHz). The initial choice for the amount of ripple current may seem arbitrary, but it serves as a good starting point for finding a standard off-the-shelf inductor value, such as  $10 \,\mu\text{H}$ ,  $15 \,\mu\text{H}$ ,  $22 \,\mu\text{H}$ ,  $33 \,\mu\text{H}$ , and  $47 \,\mu\text{H}$ . If a specific inductance value is to be used, simply rearrange Equation 2 to find the ripple current. For an  $800 \,\text{mA}$ ,  $12 \,\text{V}$  to  $5 \,\text{V}$  system, and a ripple current of  $320 \,\text{mA}$  ( $40\% \,\text{of} \,800 \,\text{mA}$ ) is chosen, the inductance is

$$L = \frac{12-5}{0.32} \times \frac{1}{200 \times 10^3} \times \frac{5}{12} = 45.5 \,\mu\text{H}$$

A 47  $\mu$ H inductor is the closest standard value that gives a ripple current of about 310 mA. The peak switch current is equal to the load current plus one-half the ripple current (this is also the peak current for the inductor and the catch diode).

$$I_{SW(PK)} = I_{OUT(MAX)} + \frac{1}{2}I_{RIPPLE} = 0.8 + 0.155 = 0.95 \text{ A}$$

(3)

Pick an inductor with a dc (or saturation) current rating about 20% larger than  $I_{\text{SW(PK)}}$  to ensure that the inductor is not running near the edge of saturation. For this example,  $1.20\times0.95~A=1.14~A,$  use an inductor with a dc current rating of at least 1.2 A. The maximum switch current is internally limited to 1.5 A, and this limit, along with the ripple current, determines the maximum load current the system can provide.

If the load current decreases to below one-half the ripple current, the regulator operates in discontinuous mode.

#### **Discontinuous Mode**

For load currents less than approximately 0.5 A, discontinuous mode operation can be used. This allows the use of a smaller inductor, but the ripple current is much higher (which means a higher output ripple voltage). If a larger output capacitor must be used to reduce the output ripple voltage, the overall system may take up more board area than if a larger inductor is used. The operation and equations for the two modes are quite different, but the boundary between these two modes occurs when the ripple current is equal to twice the load current (when  $I_{RIPPLE} = 2 \times I_{OUT}$ ). From this, Equation 2 is used to find the minimum inductor value needed to keep the system in continuous mode operation (solve for the inductor value with  $I_{RIPPLE} = 2 \times I_{OUT}$ ).

$$L_{DIS} = \frac{V_{IN(MAX)} - V_{OUT}}{2 \times I_{OUT}} \times \frac{1}{f_{SW}} \times \frac{V_{OUT}}{V_{IN(MAX)}}$$

(4)

Using an inductor below this value causes the system to operate in discontinuous mode.

For a 400 mA, 24 V to 5 V system

$$L_{DIS} \le \frac{24-5}{2\times0.4} \times \frac{1}{200\times10^3} \times \frac{5}{24} \le 24.7 \,\mu\text{H}$$

If the chosen inductor value is too small, the internal current limit trips each cycle and the regulator has trouble providing the necessary load current.

# **Inductor Core Types and Materials**

Many types of inductors are currently available. Numerous core styles along with numerous core materials often make the selection process seem even more confusing. A quick overview of the types of inductors available makes the selection process a little easier to understand.

Open core geometries (bobbin core) are usually less expensive than closed core geometries (toroidal core) and are a good choice for some applications, but care must be taken when they are used. In open core inductors, the magnetic flux is not completely contained inside the core. The radiating magnetic field generates electromagnetic interference (EMI), often inducing voltages onto nearby circuit board traces. These inductors may not be suitable for systems that contain very high accuracy circuits or sensitive magnetics. A few manufacturers have semiclosed and shielded cores, where an outer magnetic shield surrounds a bobbin core. These devices have less EMI than the standard open core and are usually smaller than a closed core.

Most core materials used in surface-mount inductors are either powdered iron or ferrite. For many designs, material choice is arbitrary, but the properties of each material should be recognized. Ferrites have lower core losses than powdered iron, but the lower loss means a higher price. Powdered iron cores saturate softly (the inductance gradually reduces as current rating is exceeded), whereas ferrite cores saturate much more abruptly (the inductance rapidly reduces). Kool  $M\mu^{\ast}$  is one type of ferrite that is specially designed to minimize core losses and heat generation (especially at switching frequencies above 100 kHz), but again, these devices are more expensive.

The winding dc resistance (DCR) of the inductor must not be overlooked. A high DCR can decrease system efficiency by 2% to 5% for lower output voltages at heavy loads. To obtain a lower DCR means using a physically larger inductor, so a tradeoff in size and efficiency must be made. The power loss due to this resistance is  $I_{\rm OUT}^2 \times$  DCR. For an 800 mA, 5 V to 3.3 V system with an inductor DCR of 100 m $\Omega$ , the winding resistance dissipates

$(0.82~A)^2 \times 0.1~\Omega = 64$  mW. This represents a power loss to the system of 64 mW/(3.3 V  $\times$  800 mA) = 2.4%. Typical DCR values are between 10 m $\Omega$  and 200 m $\Omega$ .

#### Choosina an Inductor

Several considerations must be made when choosing an inductor: cost, size, EMI, core and copper losses, and maximum current rating. Use the following steps to choose an inductor that is right for the system (refer to the calculations and descriptions

in the Inductor Selection section). Contact the manufacturers for their full product offering, availability, and pricing. The manufacturers offer many more values and package sizes to suit numerous applications.

- 1. Choose a mode of operation, then calculate the inductor value using the appropriate equation. For continuous mode systems, a ripple current of 40% of the maximum load current is a good starting point. The inductor value can then be increased or decreased, if desired.

- 2. Calculate the peak switch current (this is the maximum current seen by the inductor). Make sure that the dc (or saturation) current rating of the inductor is high enough (around 1.2× the peak switch current). Inductors with dc current ratings of at least 1 A should be used for all designs. This provides a safety margin for start-up and fault conditions where the inductor current is higher than normal. If the current rating of an inductor is exceeded, the core saturates, causing the inductance value to decrease and the temperature of the inductor to increase.

- 3. Estimate the dc winding resistance based on the inductance value. A general rule is to allow approximately 5 m $\Omega$  of resistance per  $\mu H$  of inductance.

- 4. Pick the core material and type. First, decide if an open-core inductor can be used with the design. If this cannot be determined, try a few samples of each type (open core, semi closed core, shielded core, and closed core). Do not be discouraged from using open core inductors because they require extra care; just be aware of what to look for if used. They are quite small and inexpensive, and are used successfully in many different applications.

# **OUTPUT CAPACITOR SELECTION**

The ADP3050 can be used with any type of output capacitor. The trade-offs between price, component size, and regulator performance can be evaluated to determine the best choice for each application. The effective series resistance (ESR) of the capacitor plays an important role in both the loop compensation and the system performance. The ESR provides a 0 in the feedback loop; therefore, the ESR value must be known so the loop can be compensated correctly (most manufacturers specify maximum ESR in their data sheets). The capacitor ESR also contributes to the output ripple voltage ( $V_{\text{RIPPLE}} = \text{ESR} \times I_{\text{RIPPLE}}$ ). Solid tantalum or multilayer ceramic capacitors are recommended, providing good performance with a small size and reasonable cost.

Solid tantalum capacitors have a good combination of low ESR and high capacitance, and are available from several different manufacturers. Capacitance values from 22  $\mu F$  to more than 500  $\mu F$  can be used, but values of 47  $\mu F$  to 220  $\mu F$  are sufficient for most designs. A smaller value can be used, but ESR is size-dependent, so a smaller device has a higher ESR. Ensure that the ripple current of the capacitor rating is larger than the inductor ripple current (the ripple current flows into the output capacitor).

Multilayer ceramic capacitors can be used in applications where minimum output voltage ripple is a priority. They have a very

low ESR (a 22  $\mu F$  ceramic can have an ESR one-fifth that of a 22  $\mu F$  solid tantalum), but may require more board area for the same value of output capacitance. A few manufacturers have recently improved upon their low voltage ceramic capacitors, providing a smaller package with a lower ESR (NEC Tokin, Murata, Taiyo Yuden, and AVX). Several ceramics can be used in parallel to give an extremely low ESR and a good value of capacitance. If the design is cost sensitive and not severely space limited, several aluminum electrolytic capacitors can be used in parallel (their size and ESR are larger than ceramic and solid tantalum). OS-CON capacitors can also be used, but they are typically larger and more expensive than ceramic or solid tantalum capacitors.

# **Choosing an Output Capacitor**

Use the following steps to choose an appropriate capacitor.

- 1. Decide the maximum output ripple voltage for the design, and this determines your maximum ESR (remember that  $V_{\text{RIPPLE}} \approx \text{ESR} \times I_{\text{RIPPLE}}$ ). Typical output ripple voltages range between 0.5% and 2% of the output voltage. To lower the output voltage ripple, there are only two choices: either increase the inductor value, or use an output capacitor with a lower ESR.

- Decide what type of capacitor to use (tantalum, ceramic, or others). Many more values, sizes, and voltage ratings are available, so contact each manufacturer for a complete product list. If a certain type of capacitor must be used and space permits, use several devices in parallel to reduce the total ESR.

- 3. Check the capacitor voltage rating and ripple current rating to ensure it works for the application in question. These ratings are derated for higher temperatures, so always check the manufacturer's data sheet.

- 4. Make sure the final choice for the output capacitor has been optimized for cost, size, availability, and performance yet still meets the required capacitance. The recommended capacitance is in the 47 μF to 220 μF range.

# **CATCH DIODE SELECTION**

The recommended catch diode is a Type 1N5818 Schottky or equivalent. The low forward voltage drop (450 mV typical at

**Table 4. Manufacturers**

| Inductor Manufacturers      | Capacitor Manufacturers | Schottky Diode Manufacturers |

|-----------------------------|-------------------------|------------------------------|

| Sumida                      | AVX                     | Motorola                     |

| Coilcraft                   | Kemet                   | Diodes, Inc.                 |

| Cooper Bussmann Coiltronics | Murata                  | International Rectifier      |

| NEC Tokin                   | Nemco                   | Nihon Inter Electronics      |

| Würth Elektronik            | Vishay Sprague          |                              |

| Toko                        | NEC Tokin               |                              |

|                             | Taiyo Yuden             |                              |

1 A) and fast switching speed of a Schottky rectifier provide the best performance and efficiency. The 1N5818 is rated at 30 V reverse voltage and 1 A average forward current. For lower input voltages, use a lower voltage Schottky to reduce the diode forward voltage drop and increase overall system efficiency; for example, a 12 V to 5 V system does not need a 30 V diode. For automotive applications, a 60 V Schottky may be necessary. The average forward current for the catch diode is calculated by

$$I_{DIODE(AVG)} = I_{OUT} \times \frac{V_{IN} - V_{OUT}}{V_{IN}}$$

(5)

For the earlier continuous mode example (12 V to 5 V at 800 mA), the average diode current is

$$I_{DIODE(AVG)} = 0.8 \times \frac{12 - 5}{12} = 0.47 \,\text{A}$$

(6)

For this system, a 1N5817 is a good choice (rated at 20 V and 1 A). Do not use catch diodes rated less than 1 A. Even though the average current can be less than 1 A under normal operating conditions, as the diode current is much higher under fault conditions. The worst-case fault condition for the diode occurs when the regulator becomes slightly overloaded (sometimes called a soft short). This is usually only a problem when the input voltage to output voltage ratio is greater than 2.5. Under this condition, the load current needed is slightly more than the regulator can provide. The output voltage droops slightly, and the switch stays on every cycle until the internal current limit is reached. Under this condition, the load current can reach around 1.2 A. For example, when using a system with an input voltage of 24 V and an output voltage of 5 V, if a gradual overload causes the output voltage to droop to 4 V, the average diode current is

$$I_{DIODE(AVG)} = 1.2 \times \frac{24 - 4}{24} = 1.0 \text{ A}$$

(7)

If the system must survive such gradual overloads for a prolonged period of time, ensure the diode chosen can survive these conditions. A larger 2 A or 3 A diode can be used if necessary.

#### **Choosing a Catch Diode**

Use the following steps to pick an appropriate catch diode. Table 5 shows several Schottky rectifiers with different reverse voltage and forward current ratings.

The average diode current rating must be sufficient to provide the required load current (see the calculations in the previous section). Diodes rated below 1 A should not be used, even if the average diode current is much lower.

The reverse voltage rating of the catch diode should be at least the maximum input voltage. Often a higher rating is chosen (1.2× the maximum input voltage) to provide a safety margin.

Table 5. Schottky Diode Selection Guide

| $\mathbf{V}_{R}$ | 1 A     | 2 A    | 3 A  |

|------------------|---------|--------|------|

| 15 V             | 10BQ15  | 30BQ15 |      |

| 20 V             | 1N5817  | B220   | SK32 |

| 30 V             | V1N5818 | B230   | SK33 |

| 40 V             | 1N5819  | B240   | SK34 |

#### INPUT CAPACITOR SELECTION

The input bypass capacitor plays an important role in proper regulator operation, minimizing voltage transients at the input and providing a short local loop for the switching current. Place this capacitor close to the ADP3050 between the IN and GND pins using short, wide traces. This input capacitor should have an rms ripple current rating of at least

$$I_{CIN(RMS)} \ge I_{OUT} \times \sqrt{\frac{V_{OUT}}{V_{IN}} - \left(\frac{V_{OUT}}{V_{IN}}\right)^2}$$

(8)

This rating is crucial because the input capacitor must be able to withstand the large current pulses present at the input of a step-down regulator. Values of 20  $\mu F$  to 50  $\mu F$  are typical, but the main criteria for capacitor selection is the ripple current and voltage ratings.

Ceramics are an excellent choice for input bypassing, due to their low ESR and high ripple current rating. Ceramics are especially suited for high input voltages and are available from many different manufacturers. Tantalums are often used for input bypassing, but precautions must be taken because they occasionally fail when subjected to large inrush currents during power-up. These surges are common when the regulator input is connected to a battery or high capacitance supply. Several manufacturers now offer surface-mount solid tantalum capacitors that are surge tested, but even these devices can fail if the current surge occurs when the capacitor voltage is near its maximum rating. For this reason, a 2:1 derating is suggested for tantalum capacitors used in applications where large inrush currents are present. For example, a 20 V tantalum should be used only for an input voltage up to 10 V. Aluminum electrolytics are the cheapest choice, but it takes several in parallel to get a good rms current rating. OS-CON capacitors have a good ESR and ripple current rating, but they are typically larger and more costly. Refer to Table 4 for a list of capacitor manufacturers.

#### **DISCONTINOUS MODE RINGING**

When operating in discontinuous mode, high frequency ringing appears at the switch node when the inductor current has decreased to zero. This ringing is normal and is not a result of loop instability. It is caused by the switch and diode capacitance reacting with the inductor to form a damped sinusoidal ringing. This ringing is usually in the range of several megahertz, and is not harmful to normal circuit operation.

#### SETTING THE OUTPUT VOLTAGE

The fixed voltage versions of the ADP3050 (3.3 V and 5 V) have the feedback resistor divider included on-chip. For the adjustable version, the output voltage is set using two external resistors. Referring to Figure 25, pick a value for R1 between 10 k $\Omega$  and 20 k $\Omega$ , then calculate the appropriate value for R2 using the following equation:

$$R2 = R1 \times \left(\frac{V_{OUT}}{1.20} - 1\right) \tag{9}$$

It is important to note that the accuracy of these resistors directly affects the accuracy of the output voltage. The FB pin threshold variation is  $\pm 3\%$ , and the tolerances of R1 and R2 add to this to determine the total output variation. Use 1% resistors placed close to the FB pin to prevent noise pickup.

# **FREQUENCY COMPENSATION**

The ADP3050 uses a unique compensation scheme that allows the use of any type of output capacitor. The designer is not limited to a specific type of capacitor or a specific ESR range. External compensation allows the designer to optimize the loop for transient response and system performance. The values for  $R_{\rm C}$  and  $C_{\rm C}$  set the pole and zero locations for the error amplifier to compensate the regulator loop.

For tantalum output capacitors, the typical system compensation values are  $R_{\rm C}=4~k\Omega$  and  $C_{\rm C}=1$  nF; for ceramics, the typical values are  $R_{\rm C}=4~k\Omega$  and  $C_{\rm C}=4.7$  nF. These values may not be optimized for all designs, but they provide a good starting point for selecting the final compensation values. Other types of output capacitors require different values of  $C_{\rm C}$  between 0.5 nF and 10 nF. Typically, the lower the ESR of the output capacitor, the larger the value for  $C_{\rm C}$ . Normal variations in capacitor ESR, output capacitance, and inductor value (due to production tolerances, changes in operating point, changes in temperature) affect the loop gain and phase response. Always check the final design over its complete operating range to ensure proper regulator operation.

Adjusting the  $R_C$  and  $C_C$  values can optimize compensation. Use the typical values above as a starting point, then try increasing and decreasing each independently and observing the transient response. An easy way to check the transient response of the design is to observe the output while pulsing the load current at a rate of approximately 100 Hz to 1 kHz. There should be some slight ringing at the output when the load pulses, but this should not be excessive (just a few rings). The frequency of this ringing

shows the approximate unity-gain frequency of the loop. Again, always check the design over its full operating range of input voltage, output current, and temperature to ensure that the loop is compensated correctly.

In addition to setting the zero location,  $R_{\rm C}$  also sets the high frequency gain of the error amplifier. If this gain is too large, output ripple voltage appears at the COMP pin (the output of the error amplifier) with enough amplitude to interfere with normal regulator operation. If this occurs, subharmonic switching results (the pulse width of the switch waveform changes, even though the output voltage stays regulated). The voltage ripple at the COMP pin should be kept below 100 mV to prevent subharmonic switching from occurring. The amount of ripple can be estimated by the following formula, where  $g_m$  is the error amplifier transconductance ( $g_m = 1250 \ \mu Mho$ ):

$$V_{COMP,RIPPLE} = (g_m \times R_C) \times (I_{RIPPLE} \times ESR) \times \frac{V_{FB}}{V_{OUT}}$$

(10)

For example, a 12 V to 5 V, 800 mA regulator with an inductor of  $L=47~\mu H$  has  $I_{\text{RIPPLE}}=310$  mA (see example from the Continuous Mode section) if a 100  $\mu F$  tantalum output capacitor with a maximum ESR of 100 m $\Omega$  and compensation values of  $R_{\text{C}}=4~k\Omega$  and  $C_{\text{C}}=1~nF$  are used. The ripple voltage at the COMP pin is

$$V_{COMP,RIPPLE} = (1250 \times 10^{-6} \times 4 \times 10^{3}) \times (0.310 \times 0.1) \times \frac{1.20}{5.0}$$

= 37.2 mV

If this ripple voltage is more than 100 mV,  $R_C$  needs to be decreased to prevent subharmonic switching. Typical values for  $R_C$  are in the range of 2  $k\Omega$  to 10  $k\Omega$ .

For output voltages greater than 5 V, it may be necessary to add a small capacitor in parallel with R2, as shown in Figure 25. This improves stability and transient response. For tantalum output capacitors, the typical value for  $C_F$  is 100 pF. For ceramic output capacitors, the typical value for  $C_F$  is 400 pF.

#### **CURRENT LIMIT/FREQUENCY FOLDBACK**

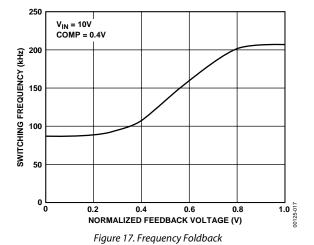

The ADP3050 uses a cycle-by-cycle current limit to protect the device under fault and high stress conditions. When the current limit is exceeded, the power switch turns off until the beginning of the next oscillator cycle. If the voltage on the feedback pin drops below 80% of its nominal value, the oscillator frequency starts to decrease (see Figure 17 in the Typical Performance Characteristics section). The frequency gradually reduces to a minimum value of approximately 80 kHz (this minimum occurs when the feedback voltage falls to 30% of its nominal value). This reduces the power dissipation in the IC, the external diode, and the inductor during short-circuit conditions. This frequency foldback method provides complete device fault protection without interfering with the normal device operation.

#### **BIAS PIN CONNECTION**

To help improve efficiency, most of the internal operating current can be drawn from the lower voltage regulated output voltage instead of the input supply. For example, if the input voltage is 24 V and the output voltage is 5 V, a quiescent current of 4 mA wastes 96 mW if drawn from the input supply, but only 20 mW is drawn from the regulated 5 V output. This power savings is most evident at high input voltages and low load currents. The output voltage must be 3 V or higher to take advantage of this feature.

# **BOOSTED DRIVE STAGE**

An external capacitor and diode are used to provide the boosted voltage needed for the special drive stage. If the output voltage is above 4 V, connect the anode of the boost diode to the regulated output; for output voltages less than or equal to voltages of  $\leq 3$  V, connect it to the input supply. For some low voltage systems, such as 5 V to 3.3 V converters, the anode of the boost diode can be connected to either the input or output voltage. During switch off time, the boost capacitor is charged up to the voltage at the anode of the boost diode. When the switch turns on, this voltage is added to the switch voltage (the boost diode is reverse-biased), providing a voltage higher than the input supply. The peak voltage appearing on the BOOST pin is the sum of the input voltage and the boost voltage (either  $V_{\rm IN}+V_{\rm OUT}$  or  $2\times V_{\rm IN}$ ). Ensure that this peak voltage does not exceed the BOOST pin maximum rating of 45 V.

For most applications, a 1N4148 or 1N914 type diode can be used with a 220 nF capacitor. A 470 nF capacitor may be needed for output voltages between 3 V and 4 V. The boost capacitor should have an ESR of less than 2  $\Omega$  to ensure that it is adequately charged up during switch off time. Almost any type of film or ceramic capacitor can be used.

# START-UP/MINIMUM INPUT VOLTAGE

For most designs, the regulated output voltage provides the boosted voltage for the drive stage. During startup, the output voltage is 0, so there is no boosted supply for the drive stage.

To deal with this problem, the ADP3050 contains a backup drive stage to get everything started. As the output voltage increases, so does the boost voltage. When the boost voltage reaches approximately 2.5 V, the switch drives transition smoothly from the backup driver to the boosted driver. If the boost voltage decreases below approximately 2.5 V, resulting in a short-circuit or overload condition, the backup stage takes over to provide switch drive. The minimum input voltage needed for the ADP3050 to function correctly is about 3.6 V (this ensures proper operation of the internal circuitry), but a small amount of headroom is needed for all step-down regulators. The following formula gives the approximate minimum input voltage needed for a given system, where  $V_{\text{SAT}}$  is the switch saturation voltage (see Figure 15 for the appropriate value of  $V_{\text{SAT}}$ ). Figure 13 also shows the typical minimum input voltage needed for 3.3 V and 5 V systems.

$$V_{IN(MIN)} = \frac{V_{OUT} + V_{SAT}}{0.85} \tag{12}$$

# THERMAL CONSIDERATIONS

Several factors contribute to IC power dissipation: ac and dc switch losses, boost current, and quiescent current. The following formulas are used to calculate these losses to determine the power dissipation of the IC. These formulas assume continuous mode operation, but they provide a reasonable estimate for discontinuous mode systems (do not use these formulas to calculate efficiency at light loads).

Switch loss

$$P_{SW} = \left(I_{OUT} \times V_{SAT} \times \frac{V_{OUT}}{V_{IN}}\right) + \left(t_{OV} \times I_{OUT} \times V_{IN} \times f_{SW}\right)$$

(13)

Boost current loss

$$P_{BOOST} = \frac{I_{OUT}}{\beta_{SW}} \times \frac{V_{OUT}^2}{V_{IN}}$$

(14)

**Quiescent current loss**

$$P_O = (V_{IN} \times I_O) + (V_{OUT} \times I_{BIAS}) \tag{15}$$

where:

$V_{SAT}$  is ~0.6 V at  $I_{OUT}$  = 800 mA (taken from Figure 15).  $f_{SW}$  is the switch frequency (200 kHz).

$t_{OV}$  is the switch current/voltage overlap time (~50 ns).  $\beta_{SW}$  is the current gain of the NPN power switch (~50).  $I_Q$  is the quiescent current drawn from  $V_{IN}$  (~1 mA).  $I_{BIAS}$  is the quiescent current drawn from  $V_{OUT}$  (~4 mA).

For example, a 5 V to 3.3 V system with  $I_{OUT} = 800 \text{ mA}$

$$P_{SW} = \left(0.8 \times 0.6 \times \frac{3.3}{5.0}\right) + \left(50 \times 10^{-9} \times 0.8 \times 5.0 \times 200 \times 10^{3}\right) = 357 \text{ mW}$$

$$P_{BOOST} = \frac{0.8}{50} \times \frac{3.3^{2}}{5.0} = 35 \text{ mW}$$

$$P_{O} = \left(5 \times 10^{-3}\right) + \left(3.3 \times 4 \times 10^{-3}\right) = 18 \text{ mW}$$

For a total IC power dissipation of

$$P_{TOTAL} = P_{SW} + P_{BOOST} + P_O = 410 \,\text{mW}$$

(16)

The ADP3050 is offered in a thermally enhanced (not Pb-free) 8-lead SOIC package with a thermal resistance,  $\theta_{JA}$ , of 60.6°C/W, and in a standard Pb-free 8-lead SOIC package with  $\theta_{JA}$  of 87.5°C/W.

The maximum die temperature, T<sub>J</sub>, is calculated using the thermal resistance and the maximum ambient temperature

$$T_{J} = T_{A} + \theta_{JA} \times P_{TOTAL} \tag{17}$$

For the previous example (5 V to 3.3 V at 800 mA system, Pb-free 8-lead SOIC package using good layout techniques) with a worst-case ambient temperature of  $70^{\circ}$ C

$$T_I = 70^{\circ}C + 87.5^{\circ}C/W \times 0.41 = 105.9^{\circ}C$$

The maximum operating junction (die) temperature is 125°C, therefore this system operates within the safe limits of the ADP3050. Check the die temperature at minimum and maximum supply voltages to ensure proper operation under all conditions. Although the PCB and its copper traces provide sufficient heat sinking, it is important to follow the layout suggestions in the Board Layout Guidelines section. For any design that combines high output current with high duty cycle and/or high input voltage, the junction temperature must be calculated to ensure normal operation. Always use the equations in this section to estimate the power dissipation.

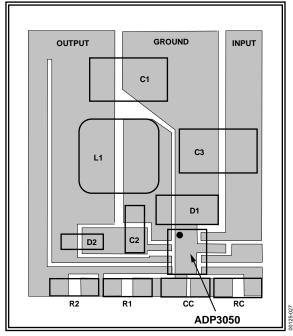

# **BOARD LAYOUT GUIDELINES**

A good board layout is essential when designing a switching regulator. The high switching currents along with parasitic wiring inductances can generate significant voltage transients and cause havoc in sensitive circuits. For best results, keep the main switching path as tight as possible (keep L1, D1, C<sub>IN</sub>, and C<sub>OUT</sub> close together) and minimize the copper area of the SWITCH and BOOST nodes (without violating current density requirements) to reduce the amount of noise coupling into other sensitive nodes.

Figure 26. Main Switching Path

The external components should be located as close to the ADP3050 as possible. For best thermal performance, use wide copper traces for all IC connections, and always connect the GND pin to a large piece of copper or ground plane. The additional copper improves heat transfer from the IC, greatly reducing the package thermal resistance. Further improvements of the thermal performance can be made by using multilayer boards and using vias to transfer heat to the other layers. A single layer board layout is shown in Figure 27. The amount of copper used for the input, output, and ground traces can be reduced, but were made large to improve the thermal performance. For the 5 V and 3.3 V versions, leave out R1 and R2; for the adjustable version, remove the trace that shorts out R2. Route all sensitive traces and components, such as those associated with feedback and compensation, away from the BOOST and SWITCH traces.

# **TYPICAL APPLICATIONS**

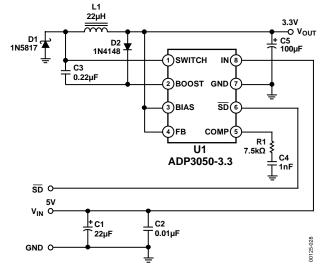

# 5 V to 3.3 V Buck (Step-Down) Regulator

The circuit in Figure 28 shows the ADP3050 in a buck configuration. It is used to generate 3.3 V regulated output from 5 V input voltage with the following specifications:

$V_{\rm IN}=4.5~V~to~5.5~V$   $V_{\rm OUT}=3.3~V$   $I_{\rm OUT}=0.75~A$   $I_{\rm RIPPLE}=0.4~A\times0.75~A=0.3~A$   $V_{\rm OUT~RIPPLE}=50~mV$

Figure 27. Recommended Board Layout

Figure 28. 5 V to 3.3 V Buck Regulator

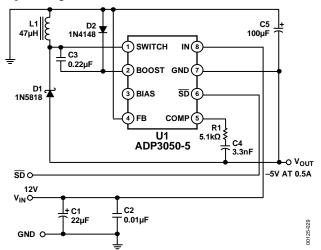

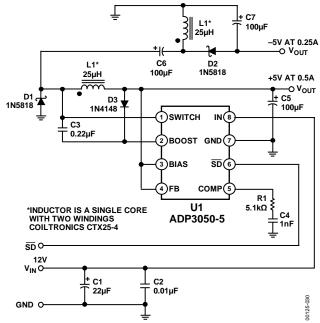

# **INVERTING (BUCK BOOST) REGULATOR**

The circuit in Figure 29 shows the ADP3050 in a buck-boost configuration that produces a negative output voltage from a positive input voltage. This topology looks quite similar to the buck shown in Figure 28 (except the IC and the output filter are now referenced to the negative output instead of ground), but its operation is quite different. For this topology, the feedback pin is grounded and the GND pin is tied to the negative output, allowing the feedback network of the IC to regulate the negative output voltage.

Figure 29. Inverting (Buck-Boost) Regulator

The design procedure used for the standard buck converter cannot be used for a buck-boost converter due to fundamental differences in how the output voltage is generated. The switch currents in the buck-boost are much higher than the standard buck converter, thus lowering the available load current. To calculate the maximum output current for a given maximum switch current, use the following equation:

$$I_{OUT(MAX)} = \frac{V_{IN}}{V_{IN} + |V_{OUT}|} \times \left[ I_{SW(MAX)} - \frac{V_{IN} \times |V_{OUT}|}{2 \times f_{SW} \times L \times (V_{IN} + |V_{OUT}|)} \right]$$

(18)

where  $I_{SW(MAX)}$  is the switch current limit rating of the ADP3050, and  $V_{IN}$  is the minimum input voltage. The inductor ripple current is estimated using the following equation:

$$I_{RIPPLE} = \frac{V_{IN(MAX)}}{L} \times \frac{1}{f_{SW}} \times \frac{\left|V_{OUT}\right|}{V_{IN(MAX)} + \left|V_{OUT}\right|}$$

(19)

For the circuit in Figure 29, the maximum ripple current (at the maximum input voltage) is

$$I_{RIPPLE} = \frac{12}{47 \times 10^{-6}} \times \frac{1}{200 \times 10^{3}} \times \frac{|-5|}{12 + |-5|} = 0.375 \,\text{A}$$

High ripple currents are present in both the input and output capacitors, and their ripple current ratings must be large enough to sustain the large switching currents present in this topology. The capacitors should have a ripple current rating of at least

$$I_{RMS(C_{IN},C_{OUT})} \approx I_{OUT} \times \sqrt{\frac{|V_{OUT}|}{V_{IN}}}$$

(20)

The peak current seen by the diode, switch, and inductor is found by rearranging the load current equation

$$I_{PEAK} = \left(\frac{V_{IN} + |V_{OUT}|}{V_{IN}} \times I_{OUT}\right) + \left(\frac{1}{2} \times I_{RIPPLE}\right)$$

(21)

The largest peak currents occur at the lowest input voltage. For this design with a load current of 500 mA